# 请注意赛普拉斯已正式并入英飞凌科技公司。

此封面页之后的文件标注有"赛普拉斯"的文件即该产品为此公司最初开发的。请注意作为英飞凌产品组合的部分,英飞凌将继续为新的及现有客户提供该产品。

# 文件内容的连续性

事实是英飞凌提供如下产品作为英飞凌产品组合的部分不会带来对于此文件的任何变更。未来的变更将在恰当的时候发生,且任何变更将在历史页面记录。

# 订购零件编号的连续性

英飞凌继续支持现有零件编号的使用。下单时请继续使用数据表中的订购零件编号。

www.infineon.com

# PSoC® 3: CY8C36 系列数据手册

# 概述

PSoC® 3 是一种真正的可编程嵌入片上系统,它在单芯片中集成了可配置的模拟和数字外设、存储器以及微控制器。PSoC 3 架构的 性能通过以下特性得到质的提升:

- 带有工作频率高达 67 MHz 的 DMA 控制器、数字滤波处理器以及 8051 内核

- 超低功耗,拥有业界最宽的工作电压范围

- 带有支持用户自定义的可编程数字和模拟外设

- ■任何模拟或数字外设端口可灵活路由至任意引脚

PSoC 器件是一个应用于嵌入式(控制)系统设计的高度灵活的可配置系统级芯片。它集成了丰富的可配置模拟和数字资源以及片上微控制器。单芯片可以实现高达上百种的模拟和数字外设功能。因此不仅可以缩短设计周期、减小电路板尺寸、降低系统功耗,还可 以在降低系统成本的基础上提升系统性能。

- ■工作特性

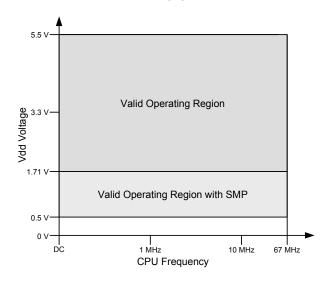

- □ 电压范围: 1.71 至 5.5 V,多达六个电压域 □ (环境)温度范围: -40 至 85°C<sup>[1]</sup>

- □ 工作频率范围: DC 至 67 MHz □ 功耗模式

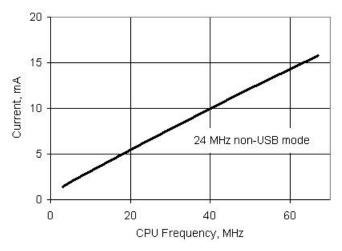

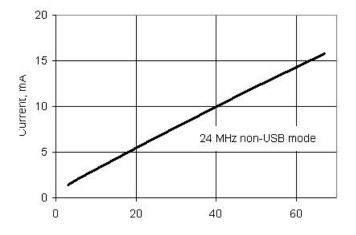

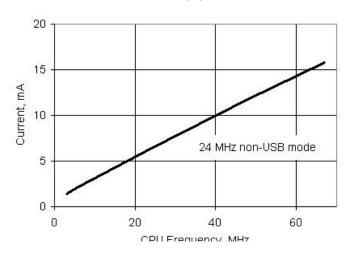

- - 在活动模式下, 频率 6 MHz 电流 1.2 mA, 频率 48 MHz 电 流 12 mA

- ・ 在睡眠模式下, 电流为 1 μA・ 在休眠模式下, 电流为 200 nA (RAM 数据保持)

- □升压调节器 (最小输入电压 0.5 V,最大输出电压 5 V)

- ■性能

- □8位8051 CPU, 32 个中断输入

- □ 24 通道直接存储器访问 (DMA) 控制器

- □ 24 位 64 抽头定点数字滤波处理器 ( DFB)

- □ 拥有缓存和安全特性的高达 64 KB 的编程闪存

- □ 高达 8KB 的用于存储纠错码(ECC)的闪存空间 □ 高达 8 KB 的 RAM

- □ 高达 2 KB 的 EEPROM

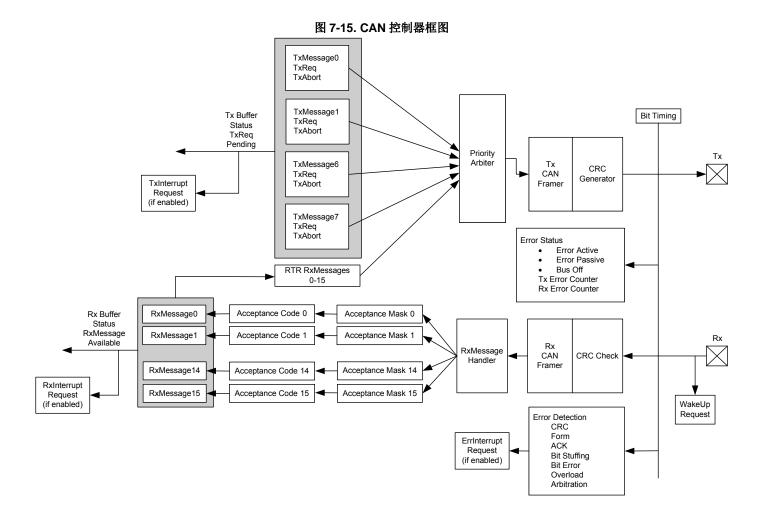

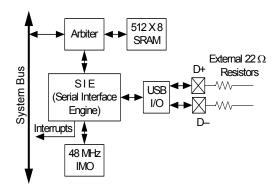

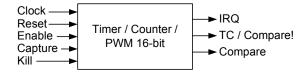

- ■数字外设

- □ 4 路 16 位定时器、计数器或 PWM 模块(TCPWM) □ 1 路硬件 I<sup>2</sup>C 模块,总线速度 1 Mbps □ 已认证的 USB 2.0 (FS) 12 Mbps 外设接口 (TID#40770053),采用内部振荡器 [2] □ 全速 CAN 2.0b 接口、16 个 Rx 缓冲区、8 个 Tx 缓冲区 □ 16 至 24 个通用数字模块(UDB),通过配置 UDB 模块,可

- 正交解码器

- 门限逻辑功能

- ■可编程时钟

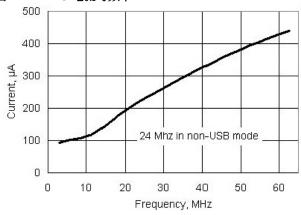

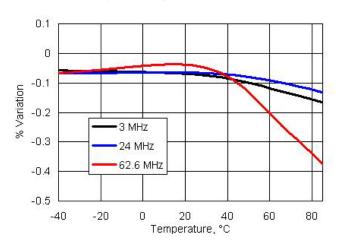

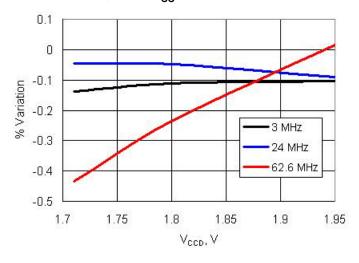

- □3到62 MHz 内部高频振荡器 (IMO), 3 MHz 输出精确度 1%

- □ 支持 4 到 25 MHz 外部晶振

- □ 67 MHz 内部 PLL 最高输出频率

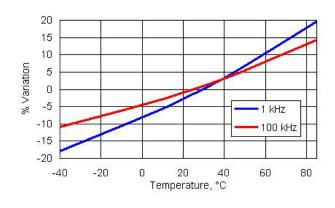

- □ 1 KHz 或 33/100 KHz 低功耗内部低频振荡器 (ILO)

- □ 32.768 kHz 的外部时钟晶振

- □ 12 个时钟分频器可路由到任何外设或 I/O

- ■模拟外设

- 8 至 12 位可配置 Delta-Sigma ADC 多达四个 8 位 DAC 多达四个比较器

- □多达四个运算放大器

- · 跨阻放大器 (TIA)

- 混频器

- 采样和保持电路 □ 支持 CapSense<sup>®</sup>,最多支持 62 个触摸传感器

- □ 1.024 V ±0.1% 内部电压参考

- □ 多功能 I/O 系统

□ 29 至 72 个 I/O 引脚 多达 62 个通用 I/O (GPIOs)

□ 多达八个特殊功能 I/O (SIO)引脚

- 25 mA 灌电流

- 可编程输入/输出阀值

- 可作为通用比较器使用

- 支持热插拔功能和过压容限

- □两个 USBIO 引脚可作为 GPIO 使用 □任意数字或模拟外设信号可以路由至任意引脚

- □ 所有 GPIO 均支持段式 LCD 驱动,最多支持 46 Com x 16 Seg

- 所有 GPIO 均支持 CapSense 功能

- □接口电压范围为 1.2 V 至 5.5 V, 多达四个电压域

- □ 支持 4线 JTAG、SWD 以及 SWV 接口 □ 支持通过 I<sup>2</sup>C、SPI、UART、USB 以及通信接口的 Bootloader 编程

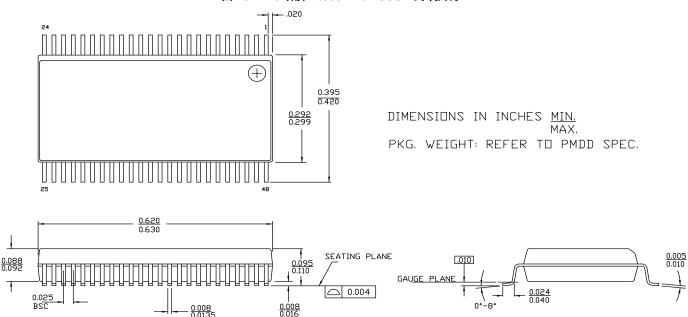

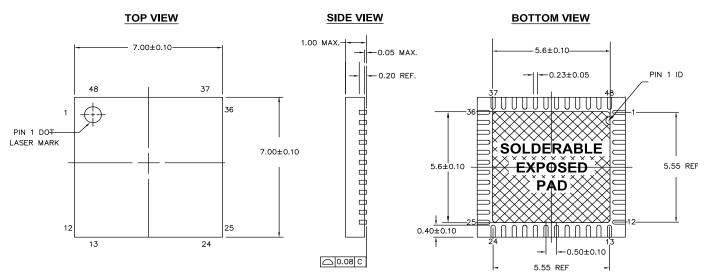

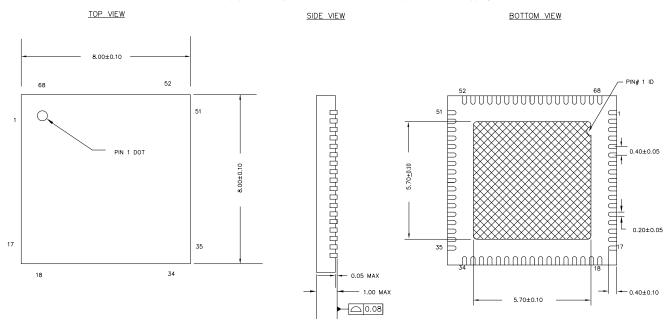

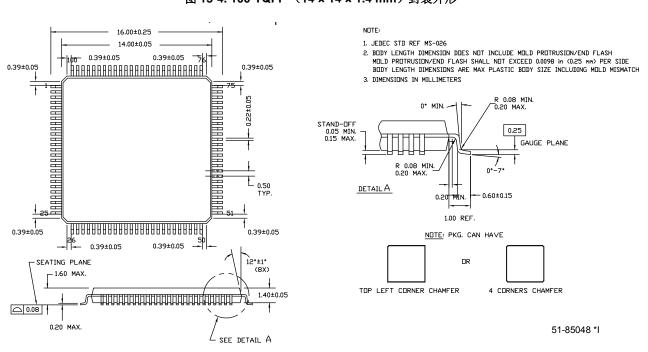

- 封装选择:: 48-SSOP、48-QFN、68-QFN、100-TQFP 以及 72-WLCSP 封装

- 支持使用免费的 PSoC Creator™ 工具进行开发

- □提供原理图和固件设计支持

- □提供了上百个 PSoC Component (PSoC 组件),相当于集成了众多专有 IC 和系统接口。每个组件均可通过简单的拖放 添加到当前设计中。

- □包含免费的 Keil 8051 编译器

- □支持器件的编程和调试

注释:

- 最大存放温度是 150°C,符合 JEDEC JESD22-A103 高温度存放使用寿命标准。

该特性仅在特定器件上提供。更多信息请参考第 120 页上的订购信息。

# 更多信息

赛普拉斯网站 www.cypress.com 上提供了大量资料,有助于选择符合您设计的 PSoC 器件,并能够快速有效地将该器件集成到您的设计中。有关使用资源的完整列表,请参考知识库文章 KBA86521 — 如何使用 PSoC 3、 PSoC 4、 PSoC 5LP 进行设计。下面是 PSoC 3 的简要列表:

概况: PSoC 产品系列, PSoC 路线图

- ■产品选择: PSoC 1、PSoC 3、PSoC 4、PSoC 5LP 另外, PSoC Creator 还包含一个器件选择工具。

- ■应用笔记 赛普拉斯提供了大量 PSoC 应用笔记,包括从基本到高级的广泛主题。下面提供了入门 PSoC 3 的推荐应用笔记:

- □ AN54181: 入门 PSoC 3

- □ AN61290: 硬件设计的注意事项

- □ AN57821: 混合信号电路板布局

- □ AN58304: 模拟设计的引脚选择

- □ AN81623: 数字设计的最佳实践

- □ AN73854: Bootloaders 的简介

- 开发套件:

- □ CY8CKIT-001: 为 PSoC 1、PSoC 3、PSoC 4 或 PSoC 5LP 器件系列提供了一个通用的开发平台。

- □ CY8CKIT-030: 是专门为模拟性能而设计的。通过该套件, 您可以评估、开发基于 PSoC3 的高精度模拟、低功耗以及低电压的各种应用。

这两种套件都支持连接 PSoC 扩展板套件。扩展套件可用于 CapSense、高精度温度测量和电源监控等多种应用。

MiniProg3 编程工具可用于对 PSoC 器件的编程和调试 (PSoC1 器件仅限编程)。

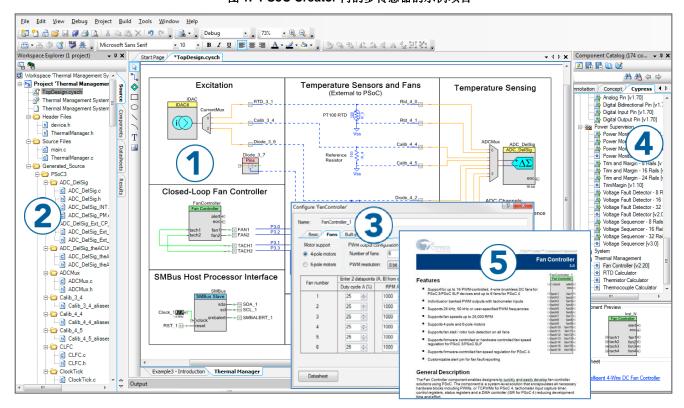

# **PSoC Creator**

PSoC Creator 是一个免费的基于 Window 的集成设计环境(IDE)。通过它能够同时在 PSoC 3、PSoC 4 和 PSoC 5LP 系统中设计 硬件和固件。PSoC Creator 通过基于原理图的经典方法设计系统架构,由上百个预验证可可用于生产的 PSoC Component tm 给与支持。更多信息请参考组件数据手册列表。使用 PSoC Creator,可以执行以下操作:

- 将组件图标施放到主要设计工作区中,以进行您的硬件系统设计。

- 2. 使用 PSoC Creator 集成开发环境编译器对您的应用固件和 PSoC 硬件进行协同设计。

- 3. 使用配置工具配置各组件

- 4. 研究包含 100 多个组件的库

- 5. 查看组件数据手册

# 图 1. PSoC Creator 内的多传感器的示例项目

# 目录

| 1. | 架构概述    |                    | . 4 |

|----|---------|--------------------|-----|

| 2. | 引脚分布    |                    | . 6 |

| 3. | 引脚说明    |                    | 12  |

| 4. | CPU     |                    | 13  |

|    |         | 1 CPU              |     |

|    |         | _模式                |     |

|    | 4.3 指令  | •集                 | 13  |

|    | 4.4 DM  | A 与 PHUB           | 17  |

|    | 4.5 中断  | f控制器               | 19  |

| 5. | 存储器     |                    | 22  |

|    | 5.1 静态  | RAM                | 22  |

|    | 5.2 闪存  | 程序存储器              | 22  |

|    | 5.3 闪存  | 安全性                | 22  |

|    |         | PROM               |     |

|    |         | 5失性锁存器 (NVL)       |     |

|    |         | 3存储器接口             |     |

|    | 5.7 存储  | <b>5器映射</b>        | 25  |

| 6. | 系统集成    |                    | 27  |

|    |         | 「系统                |     |

|    |         | !系统                |     |

|    |         | <u>f</u>           |     |

|    | 6.4 I/O | 系统与布线              | 35  |

| 7. | 数字子系统   | 充                  | 41  |

|    |         | t示例                |     |

|    | 7.2 通用  | ]数字模块              | 44  |

|    |         | 3 阵列说明             |     |

|    |         | 走线接口说明             |     |

|    |         | N                  |     |

|    |         | 3                  |     |

|    |         | 器、计数器和 PWM         |     |

|    |         | - NENA 111 144 I.L |     |

|    |         | · 滤波器模块            |     |

| 8. |         | 统                  |     |

|    |         | l 布线               |     |

|    |         | a-sigma 模数转换器      |     |

|    |         | · 器                |     |

|    |         | I放大器               |     |

|    |         | 諸程 SC/CT 模块        |     |

|    |         | ) 直接驱动器            |     |

|    |         | Sense              |     |

|      | 8.9 DAC               |    |

|------|-----------------------|----|

|      | 8.10 上变频 / 下变频混频器     | 62 |

|      | 8.11 采样和保持电路          | 63 |

| 9. ≰ | 扁程、调试接口与资源            | 63 |

| •    | 9.1 JTAG 接口           |    |

|      | 9.2 串行线调试接口           |    |

|      | 9.3 调试功能              | 66 |

|      | 9.4 跟踪特性              |    |

|      | 9.5 单线浏览器接口           | 66 |

|      | 9.6 编程功能              | 66 |

|      | 9.7 器件安全性             |    |

|      | 9.8 CSP 封装 Bootloader | 67 |

| 10.  | 开发支持                  | 68 |

|      | 10.1 文档               |    |

|      | 10.2 在线资源             |    |

|      | 10.3 工具               | 68 |

| 11.  | 电气规范                  |    |

|      | 11.1 最大绝对额定值          |    |

|      | 11.2 芯片级规范            |    |

|      | 11.3 电源调节器            |    |

|      | 11.4 输入和输出            |    |

|      | 11.5 模拟外设             |    |

|      | 11.6 数字外设 1           |    |

|      | 11.7 存储器 1            |    |

|      | 11.8 PSoC 系统资源 1      |    |

|      | 11.9 时钟 1             |    |

| 12.  | 订购信息1                 |    |

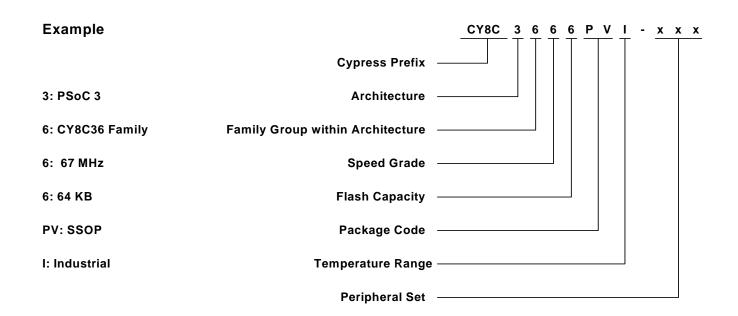

|      | 12.1 器件编号约定 1         | 21 |

| 13.  | 封装1                   | 22 |

| 14.  | 缩略语1                  | 26 |

| 15.  | 参考文档1                 | 27 |

| 16.  | 文档规范1                 | 28 |

|      | 16.1 测量单位 1           |    |

| 17.  | 修订记录1                 |    |

|      | 销售、解决方案和法律信息          |    |

|      | 全球销售和设计支持1            |    |

|      | 产品                    |    |

|      | PSoC® 解决方案1           |    |

|      | 赛普拉斯开发者社区 <b>1</b>    |    |

|      |                       | 20 |

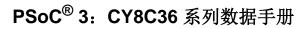

# 1. 架构概述

CY8C36 系列的超低功耗闪速可编程片上系统(PSoC®)器件是可扩展的 8 位 PSoC 3 和 32 位 PSoC 5 平台的一部分。CY8C36 系列提供了与 CPU 子系统相关的可配置模拟块、数字和互连电路模块。通过将 CPU 同高度灵活的模拟子系统、数字子系统、布线及 I/O 相结合,可以在众多消费、工业和医疗应用场合实现高度集成。

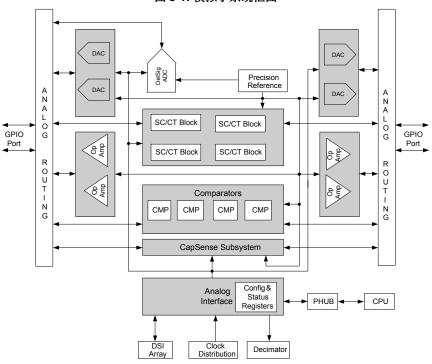

图 1-1. 简化框图

图 1-1 显示了 CY8C36 系列的主要组件, 其中包括:

- 8051 CPU 子系统

- ■非易失性存储子系统

- ■编程、调试和测试子系统

- ■输入和输出

- ■时钟

- ■功耗

- ■数字子系统

- ■模拟子系统

PSoC 具有独特的可配置性,其中有一半是由其数字子系统提供的。数字子系统不仅能够通过数字系统互连(DSI)将来自任意外设的数字信号连接至任意引脚,而且还能够通过小而快的低功耗 UDB 实现功能灵活性。PSoC Creator 提供了一个外设库,其中包括经过测试并已映射至 UDB 阵列的标准预建数字外设,如UART、SPI、LIN、PRS、CRC、定时器、计数器、PWM、AND、OR等。此外,您还可以通过图形设计输入的方式,使用底层逻辑元件库轻松创建数字电路。每个 UDB 均包含可编程阵列逻辑(PAL)/可编程逻辑器件(PLD)功能,以及支持众多外设的小型状态机引擎。

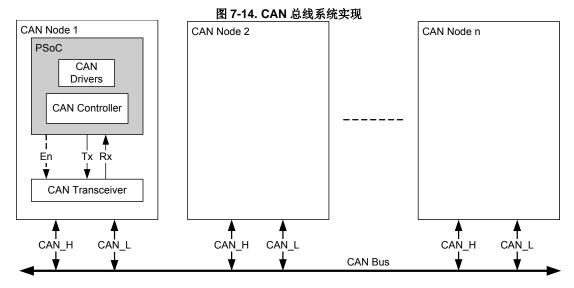

除了能够提高 UDB 阵列的灵活性之外, PSoC 还提供旨在实现特定功能的可配置数字模块。对于 CY8C36 系列, 这些模块可包括四个 16 位定时器、计数器和 PWM 模块、 I<sup>2</sup>C 从、主和多主接口、全速 USB 以及全速 CAN 2.0b。

有关外设的详细信息,请参见本数据手册的第 41 页上的外设示例。有关 UDB、DSI 及其他数字模块的信息,请参见本数据手册的第 41 页上的数字子系统一节。

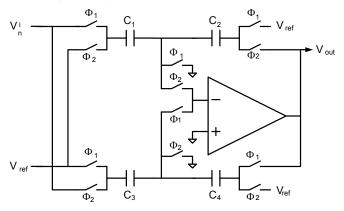

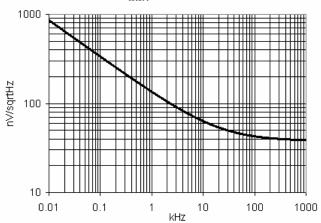

PSoC 独特可配置性的另外一半则来自于其模拟子系统。所有模拟性能都基于高度精确的绝对电压参考(在有效工作温度和电压下误差小于 0.1%)。可配置模拟子系统包括:

- ■模拟复用器

- ■电压比较器

- 电压参考

- ■模数转换器 (ADC)

- 数模转换器 (DAC)

- ■数字滤波器模块 (DFB)

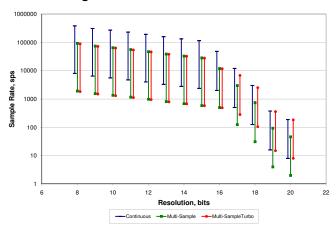

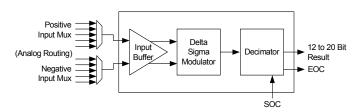

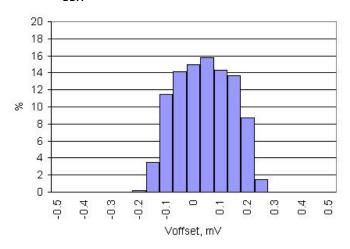

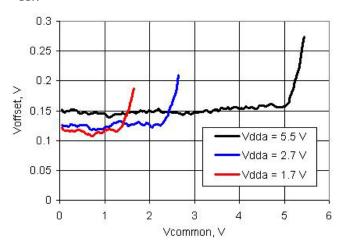

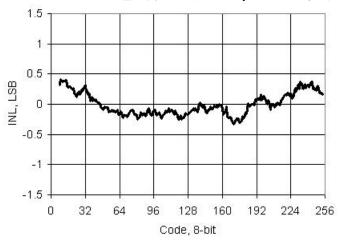

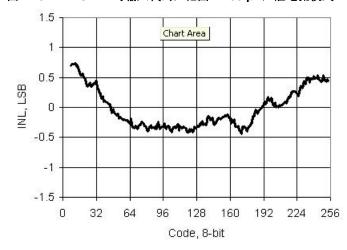

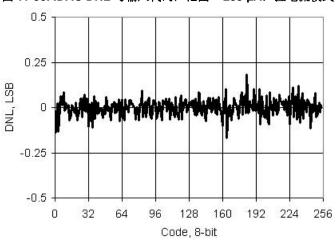

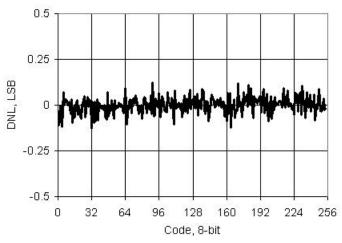

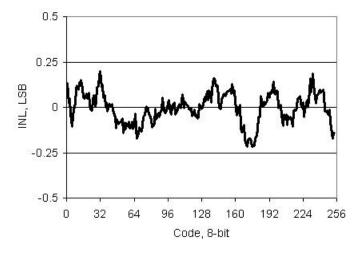

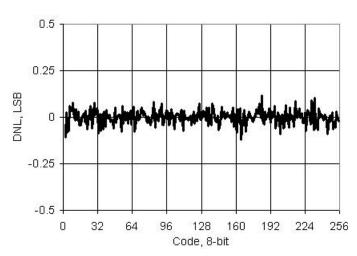

所有 GPIO 引脚都可以使用内部模拟总线将模拟信号输入和输出器件。因此,器件可接多达 62 个分立模拟信号。模拟子系统中包含一个快速、精确并具有以下特性的可配置 Delta-Sigma ADC:

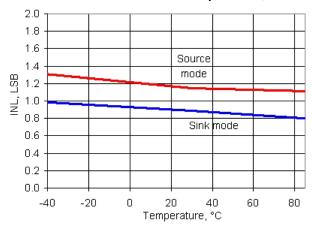

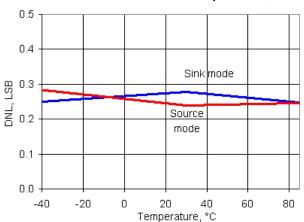

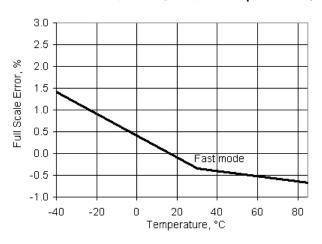

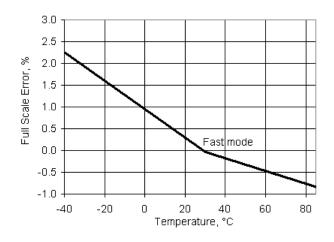

- 偏移小于 100 µV

- 增益误差为 0.2%

- INL 小于 ±1 LSB

- DNL 小于 ±1 LSB

- SINAD 优于 66 dB

该转换器能够满足众多高精度模拟应用的需求,其中包括一些要 求最为严苛的传感器。

可以通过 DMA 选择任意 ADC 的输出提供给可编程 DFB,而没有 CPU 的干预。可配置 DFB 以执行 IIR 和 FIR 数字滤波器以及某些用户定义的功能。 DFB 可用最大 64 个抽头实现过滤。它可在一个时钟周期中执行 48 位乘累加(MAC)操作。

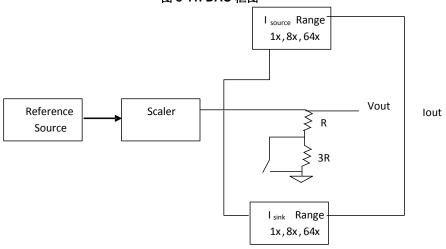

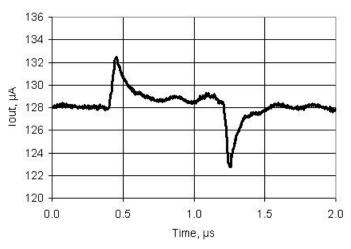

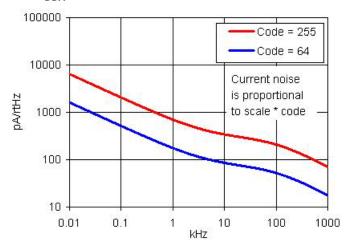

四个高速电压 DAC 或电流 DAC 支持 8 位输出信号,其更新速率最高可达 8 Msps。它们可以路由到任何 GPIO 引脚。您可以使用UDB 阵列创建分辨率更高的电压 PWM DAC 输出。利用此方法,可以在高达 48 kHz 的频率下创建高达 10 位的 PWM DAC。每个UDB 中的数字 DAC 都支持 PWM、PRS 或 delta-sigma 算法,并且宽度可编程。

除了 ADC、 DAC 和 DFB 以外,模拟子系统还提供:

- ■多个运算放大器

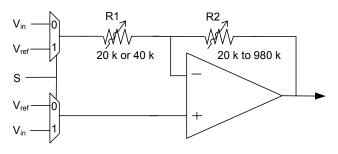

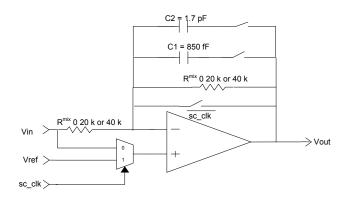

- 多个可配置的开关电容 / 连续时间 (SC/CT) 模块。这些模块支持:

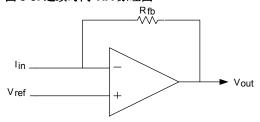

- □互阻放大器

- □可编程增益放大器

- □混频器

- □其他类似模拟组件

有关详细信息,请参见本数据手册的第54页上的模拟子系统。

PSoC 的 8051 CPU 子系统是围绕工作频率高达 67 MHz 的单周期流水线 8051 8 位处理器构建的。CPU 子系统包括可编程的嵌套向量中断控制器、DMA 控制器和 RAM。PSoC 的嵌套向量中断控制器可让 CPU 直接前进到中断服务例程的第一个地址,而无需在其他架构中使用的跳转指令,因此具有较低的延迟。DMA 控制器使外设能够在没有 CPU 干预的情况下交换数据。这样一来,CPU 就能够以较慢的速度运行(降低功耗)或使用这些 CPU 周期来提高固件算法的性能。单周期 8051 CPU 的运行速度比标准 8051 处理器快十倍。处理器速度本身是可以配置的,从而能够针对特定应用调整运行功耗。

PSoC 的非易失性子系统由闪存、按字节写入的 EEPROM 以及非易失性配置选项构成。它能够提供高达 64 KB 的片上闪存。CPU 可以对闪存的各个区块重新进行编程,以便使能Bootloader。您可以针对可靠性较高的应用使能纠错码。功能强大且非常灵活的保护模型能够保护用户的敏感信息,并能够锁定选定的存储器模块,以便实现读写保护。片上提供了高达 2 KB的按字节写入的 EEPROM,用于存储应用程序数据。此外,选定的配置选项(如引导速度和引脚驱动模式)存储在非易失性存储器中,以便在加电复位(POR)后立即激活相关设置。

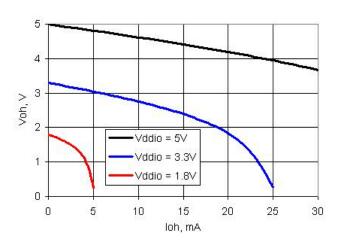

三种类型的 PSoC I/O 都非常灵活。所有 I/O 都具有多种可在上电复位时设置的驱动模式。 PSoC 还通过 VDDIO 引脚提供多达四个 I/O 电压域。每个 GPIO 都具有模拟 I/O、LCD 驱动 <sup>[3]</sup>、CapSense<sup>[4]</sup>、灵活的中断生成、转换速率控制以及数字 I/O 功能。PSoC 上的 SIO 允许在用作输出时独立设置 V<sub>OH</sub> 和 V<sub>DDIO</sub>。SIO 在输入模式下处于高阻抗状态。即使当器件未加电或引脚电压高于供电电压时,亦是如此。这使得 SIO 非常适合在 I<sup>2</sup>C 总线上使用,因为当该总线上的其他器件处于加电状态时,PSoC 可能未加电。SIO 引脚还具有非常高的灌电流能力,适用于 LED 驱动等应用。通过使用 SIO 的可编程输入阈值特性,可以将 SIO 用作通用模拟电压比较器。此外,对于带全速 USB 的器件,还提供了 USB 物理接口(USBIO)。当不使用 USB 时,这些引脚还可以用于实现有限的数字功能和进行器件编程。本数据手册的第35 页上的 I/O 系统与布线对 PSoC I/O 的所有特性进行了详细说明

PSoC 器件集成了非常灵活的内部时钟生成器,能够实现高度的稳定和精度。内部主振荡器(IMO)是系统的时基,在 3 MHz 下的精度为 1%。可对 IMO 进行配置,使之在 3 MHz 至 62 MHz 的工作频率范围内运行。为满足应用的要求,可将主时钟频率分频成多个时钟。器件提供了一个 PLL,以便从 IMO、外部晶振或外部参考时钟生成高达 67 MHz 的时钟频率。器件还包含一个单独的超低功耗内部低速振荡器(ILO),以便供睡眠和看门狗定时器使用。此外,在实时时钟(Real Time Clock,RTC)应用中,还支持使用 32.768 kHz 的外部时钟晶体。时钟以及可编程时钟分频器具有高度的灵活性,能够满足大多数时序要求。

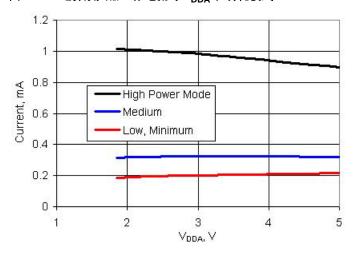

CY8C36 系列能够在 1.71 至 5.5 V 的电压范围内工作。这样,可以采用 1.8 V ± 5%、 2.5 V ±10%、 3.3 V ± 10% 或 5.0 V ± 10%等稳压电源,或直接采用多种不同类型的电池。此外,该系列还提供了一个集成的高效同步升压器,能够采用低至 0.5 V 的供电电压为器件供电。这样一来,便可以通过单个电池或太阳能电池为器件直接供电。不仅如此,您还可以使用升压转换器来生成器件所需的其他电压,例如,驱动 LCD 显示屏所需的 3.3 V 电压。升压器的输出引脚是 V<sub>BOOST</sub>,从而可以从 PSoC 为应用中的其他器件供电。

PSoC 支持多种低功耗模式,其中包括 200 nA 休眠模式 (RAM 保留数据)和 1  $\mu$ A 睡眠模式 (RTC 保持运行)。在第二种模式下,可选的 32.768 kHz 时钟晶体会连续运行,以保持精确的RTC。

对所有主要功能模块(包括可编程数字和模拟外设)的供电可由固件独立控制。因此,当某些外设未被使用时,可以采用低功耗后台处理模式。这样一来,CPU 在 6 MHz 下运行时,器件总电流仅为 1.2 mA,或者在 3 MHz 下则仅为 0.8 mA。

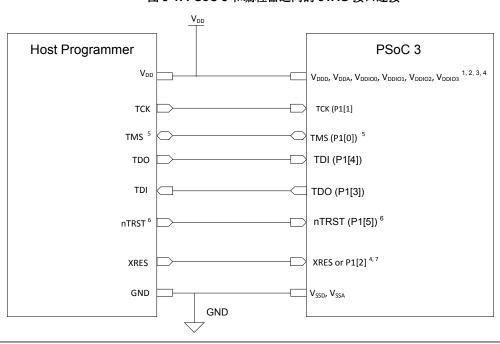

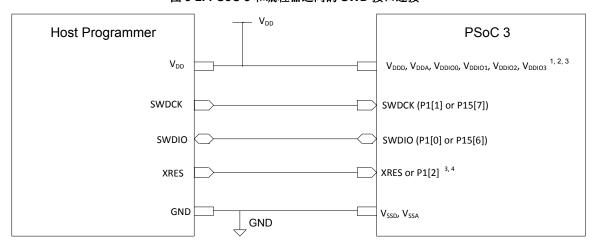

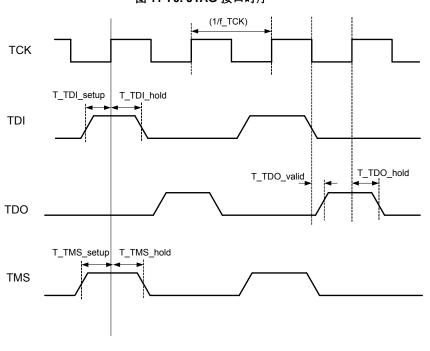

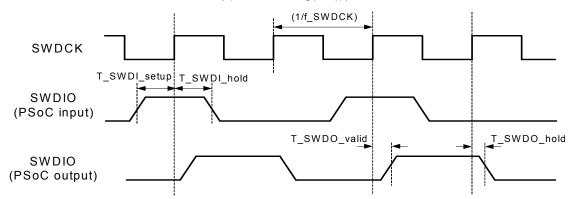

关于 PSoC 功耗模式的详细信息,请参见本数据手册的第 30 页上的供电系统。 PSoC 采用 JTAG(4 线)接口或 SWD(2 线)接口进行编程、调试和测试。单线查看器(SWV)也可用于进行"printf"式调试。通过结合使用 SWD 和 SWV,您只需三个引脚,即可实现全功能调试接口。借助这些标准接口,您能够利用赛普拉斯公司或第三方供货商提供的众多硬件解决方案对PSoC 进行调试或编程。 PSoC 支持片上断点以及 4 KB 的指令和数据竞争存储器,以便进行调试。有关编程、测试和调试接口的详细信息,请参见本数据手册的第 63 页上的编程、调试接口与资源。

# 2. 引脚分布

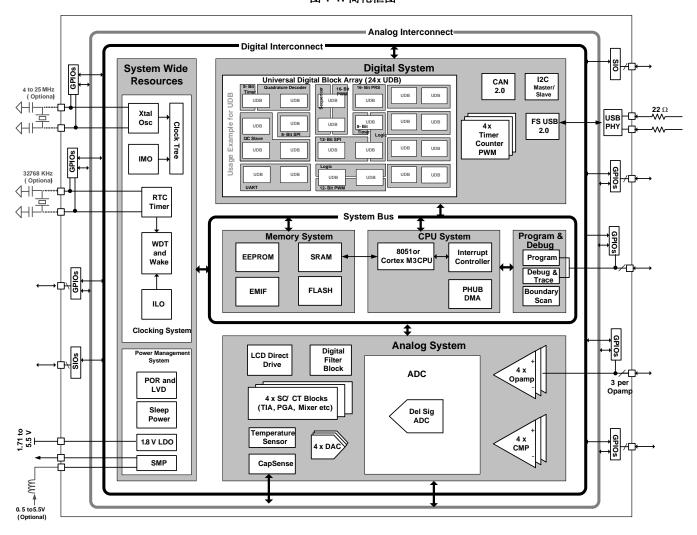

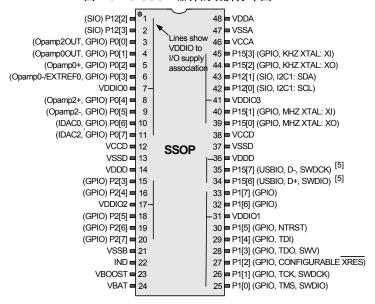

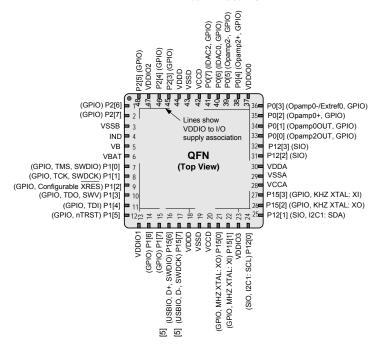

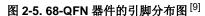

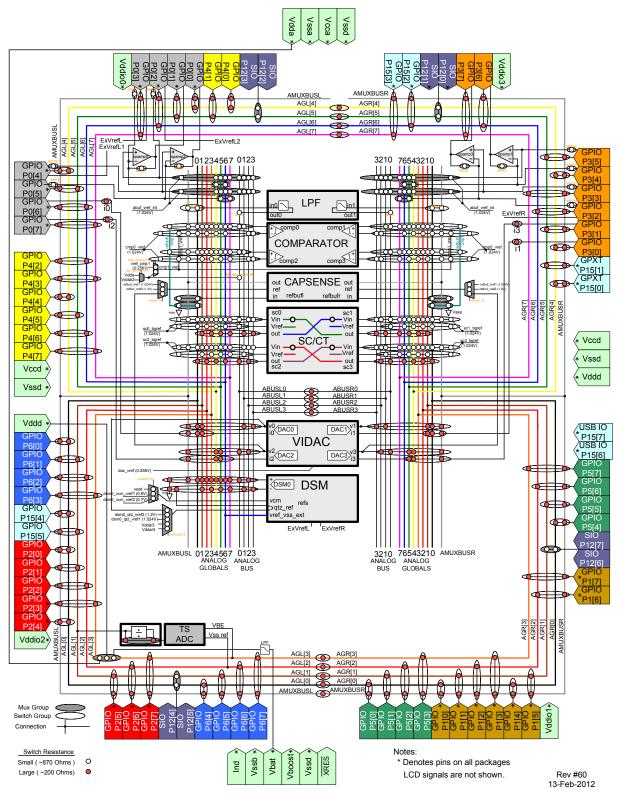

每个 VDDIO 引脚会供电给一组特殊的 I/O 引脚。(通过 VDDD 供电给 USBIO。)通过使用 VDDIO 引脚,单个 PSoC 即可支持多个接口电压电平,而无需片外电平转换器。图 2-3 到图 2-6 中引脚分配框图内的黑线显示了每个 VDDIO 所供电的引脚。

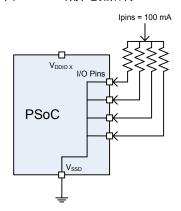

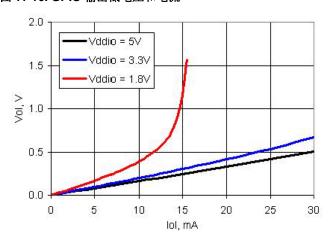

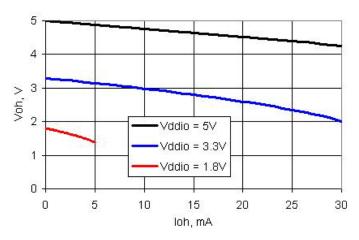

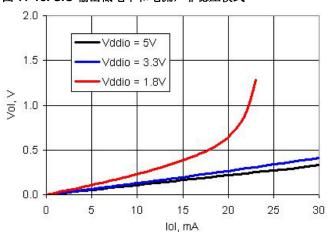

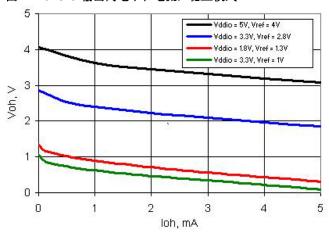

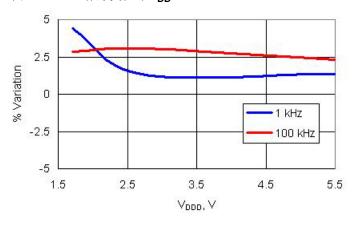

每个 VDDIO 总共可为相应 I/O 引脚提供高达  $100 \, \text{mA}$  的拉电流,如图 2-1 所示。

# 图 2-1. VDDIO 电流限制

反过来,对于 100 引脚和 68 引脚器件,也可以将 100 mA 的总电流灌入到与任意 VDDIO 相应的引脚组,如图 2-2 所示。

# 图 2-2. I/O 引脚电流限制

对于 48 引脚器件,可以将 100 mA 的总电流灌入到与 VDDIO0 和 VDDIO2 相应的所有 I/O 引脚组。可以将 100 mA 的总电流灌入到与 VDDIO1 和 VDDIO3 相应的所有 I/O 引脚组。

### 注释:

- 3. 此特性仅在特定器件上提供。有关详细信息,请参见第 120 页上的订购信息。

- 4. Opamp 的固有输出引脚不建议用作 CapSense 功能。

# 图 2-3. 48-SSOP 器件的引脚分布图

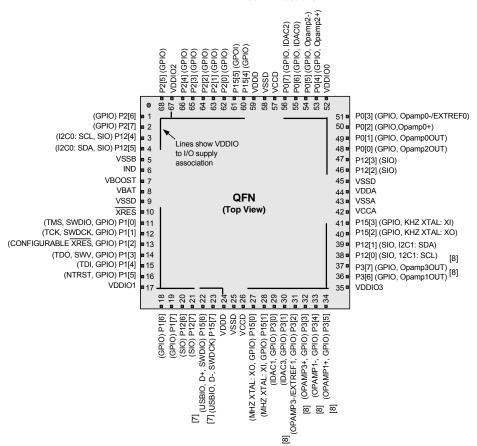

# 图 2-4. 48-QFN 器件的引脚分布图 [6]

### 注释

- 5. 在不带 USB 的器件上,引脚的状态为"NDU"(即请勿使用)。该引脚必须悬空。

- 6. QFN 封装上的中心焊盘应连接到数字接地(VSSD),以获得最佳机械、热学和电气性能。如果未接地,则应处于电气悬空状态,而不能连接到任何其他信号。

- 7. 在不带 USB 的器件上,引脚处于 " 请勿使用 " (DNU)状态。该引脚必须悬空。 8. 此特性仅在特定器件上提供。更多有关信息,请参考第 120 页上的订购信息。 9. QFN 封装上的中心焊盘应连接到数字接地(VSSD),以获得最佳机械、热和电气性能。如果未接地,则应处于电气悬空状态,而不能连接到任何其他信号。更多有 关信息,请参考 AN72845,QFN 器件的设计指南。

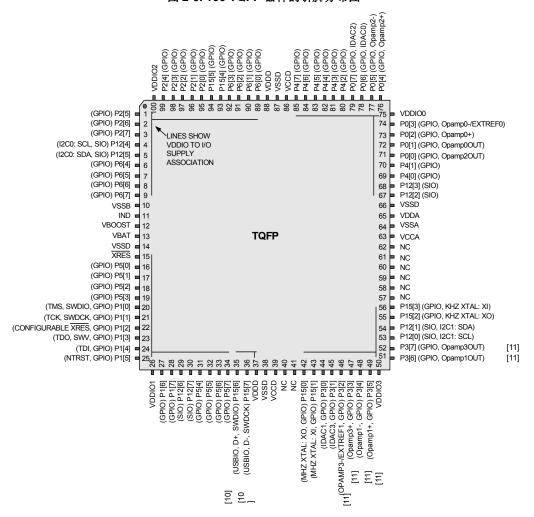

图 2-6. 100 TQFP 器件的引脚分布图

表 2-1 显示的是 72-CSP 封装的引脚分布。由于共有 4 个  $V_{DDIO}$  引脚,因此,与 100 引脚和 68 引脚器件相同,将 100 mA 的总电流 灌入到与  $V_{DDIO}$  相应的 I/O 引脚组。

表 2-1. CSP 引脚分布

| 球形焊盘 | 名称     | 球形焊盘 | 名称     | 球形焊盘 | 名称     |

|------|--------|------|--------|------|--------|

| G6   | P2[5]  | F1   | VDDD   | A5   | VDDA   |

| E5   | P2[6]  | E1   | VSSD   | A6   | VSSD   |

| F5   | P2[7]  | E2   | VCCD   | B6   | P12[2] |

| J7   | P12[4] | C1   | P15[0] | C6   | P12[3] |

| H6   | P12[5] | C2   | P15[1] | A7   | P0[0]  |

| J6   | VSSB   | D2   | P3[0]  | B7   | P0[1]  |

| J5   | Ind    | D3   | P3[1]  | B5   | P0[2]  |

| H5   | VBOOST | D4   | P3[2]  | C5   | P0[3]  |

| J4   | VBAT   | D5   | P3[3]  | A8   | VIO0   |

### 注释:

10. 在不带 USB 的器件上,引脚的状态为 "NDU" (即请勿使用)。该引脚必须悬空。

11. 此特性仅在特定器件上提供。更多有关信息,请参考第 120 页上的订购信息。

# 表 2-1. CSP 引脚分布 (续)

| 球形焊盘 | 名称     | 球形焊盘               | 名称     | 球形焊盘 | 名称     |

|------|--------|--------------------|--------|------|--------|

| H4   | VSSD   | B4                 | P3[4]  | D6   | P0[4]  |

| J3   | XRES_N | B3                 | P3[5]  | D7   | P0[5]  |

| H3   | P1[0]  | A1                 | VIO3   | C7   | P0[6]  |

| G3   | P1[1]  | B2                 | P3[6]  | C8   | P0[7]  |

| H2   | P1[2]  | A2                 | P3[7]  | E8   | VCCD   |

| J2   | P1[3]  | C3                 | P12[0] | F8   | VSSD   |

| G4   | P1[4]  | C4                 | P12[1] | G8   | VDDD   |

| G5   | P1[5]  | E3                 | P15[2] | E7   | P15[4] |

| J1   | VIO1   | E4                 | P15[3] | F7   | P15[5] |

| F4   | P1[6]  | B1 <sup>[12]</sup> | NC     | G7   | P2[0]  |

| F3   | P1[7]  | B8 <sup>[12]</sup> | NC     | H7   | P2[1]  |

| H1   | P12[6] | D1 <sup>[12]</sup> | NC     | H8   | P2[2]  |

| G1   | P12[7] | D8 <sup>[12]</sup> | NC     | F6   | P2[3]  |

| G2   | P15[6] | A3                 | VCCA   | E6   | P2[4]  |

| F2   | P15[7] | A4                 | VSSA   | J8   | VIO2   |

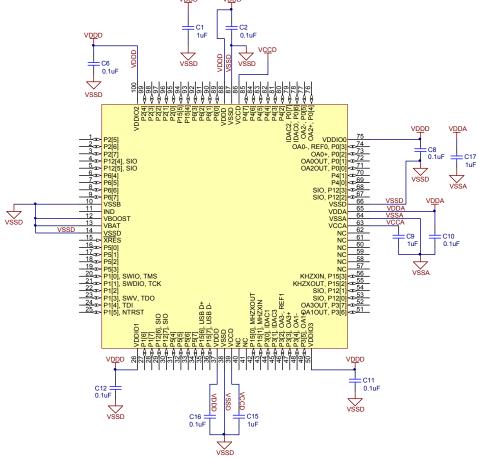

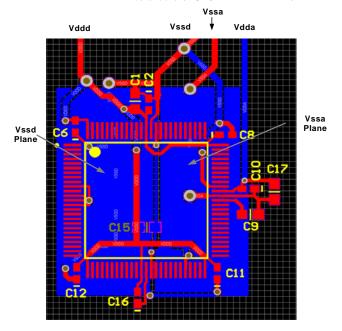

图 2-7 和第 12 页上的图 2-8 所示为 100-TQFP 器件的原理图和 PCB 布局图示例,展示了如何在两层电路板上获得最佳模拟性能。

- 两个标有 VDDD 的引脚必须连接在一起。

- 两个标有 Vccd 的引脚必须连接在一起,并且必须连接电容,如图 2-7 和第 30 页上的供电系统所示。两个 Vccd 引脚之间的线路越短越好。

- 两个标有 VSSD 的引脚必须连接在一起。

有关混合信号电路板布局问题的详细信息,请参考应用手册 AN57821 — PSoC® 3 与 PSoC 5LP 混合信号电路板布局的注意事项。

### 注释:

12. 在不带 USB 的器件上,引脚的状态为 "NDU" (即请勿使用)。该引脚必须悬空。 13. 此特性仅在特定器件上提供。更多有关信息,请参考第 120 页上的订购信息。

图 2-7. 100-TQFP 器件的原理图示例 (包含供电连接)

注意: 两个 Vccd 引脚必须连接在一起,并且之间的线路越短越好。建议在器件下方连接线路,如第 12 页上的图 2-8 所示。

图 2-8. 100-TQFP 器件获得最佳模拟性能的 PCB 布局示例

# 3. 引脚说明

**IDAC0、IDAC1、IDAC2、IDAC3.** 大电流 DAC(IDAC)的低电阻输出引脚。

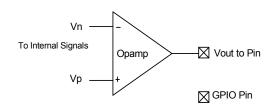

Opamp0out、Opamp1out<sup>[15]</sup>、Opamp2out、Opamp3out<sup>[15]</sup>. 运算放大器的大电流输出。<sup>[14]</sup>

Extref0、Extref1. 模拟系统的外部参考输入引脚。

**Opamp0-、Opamp1-**<sup>[15]</sup>**、Opamp2-、Opamp3-**<sup>[15]</sup>. 运算放大器的反相输入引脚。

**Opamp0+、 Opamp1+<sup>[15]</sup>、 Opamp2+、 Opamp3+<sup>[15]</sup>.** 运 算 放大器的同相输入引脚。

**GPIO.** 通用 I/O 引脚为 CPU、数字外设、模拟外设、中断、LCD 段驱动和 CapSense 提供了接口。 <sup>[14]</sup>

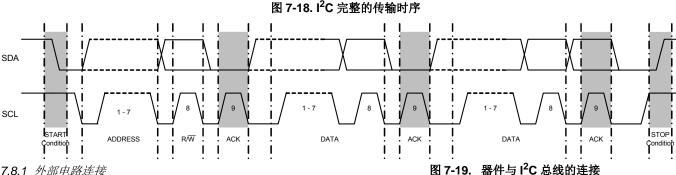

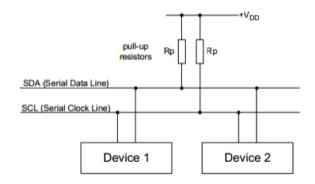

**I2C0:** SCL、I2C1: SCL. I $^2$ C SCL 线路提供在地址匹配时从睡眠模式唤醒的功能。如果不需要从睡眠模式唤醒,则任意 I/O 引脚都可用于 I $^2$ C SCL。

**I2C0: SDA、I2C1: SDA.**  $I^2$ C SDA 线路提供在地址匹配时从睡眠模式唤醒的功能。如果不需要从睡眠模式唤醒,则任意 I/O 引脚都可用于  $I^2$ C SDA。

Ind. 升压器的电感连接引脚。

kHz XTAL: Xo、kHz XTAL: Xi. 32.768 kHz 晶振引脚。

MHz XTAL: Xo、MHz XTAL: Xi. 4 - 25 MHz 晶振引脚。

nTRST. 可选的 JTAG 测试复位编程与调试端口连接引脚,用于复位 JTAG 连接。

**SIO.** 专用 I/O 提供用于连接 CPU、数字外设和中断的接口,并能够提供可编程的高阈值电压、模拟电压比较器和非常高的灌电流,当器件未加电时处于高阻抗状态。

SWDCK. 串行线调试时钟编程与调试端口连接引脚。

SWDIO. 串行线调试输入和输出编程与调试端口连接引脚。

SWV. 单线查看器调试输出引脚。

TCK. JTAG 测试时钟编程与调试端口连接引脚。

TDI. JTAG 测试数据输入编程与调试端口连接引脚。

TDO. JTAG 测试数据输出编程与调试端口连接引脚。

TMS. JTAG 测试模式选择编程与调试端口连接引脚。

USBIO、D+. 提供与 USB 2.0 总线的直接 D+ 连接。可用作数字 I/O引脚。在不带USB的器件上,引脚处于"请勿使用"(DNU)状态。

USBIO、D-. 提供与 USB 2.0 总线的直接 D- 连接。可用作数字 I/O引脚。在不带USB的器件上,引脚处于"请勿使用"(DNU)状态。

VBOOST. 升压转换器的供电传感连接引脚。

VBAT. 升压转换器的电池供电引脚。

### 注释

14. 运算放大器的固定输出引脚不建议用作 CapSense 功能

15. 此特性仅在特定器件上提供。更多有关信息,请参考第 120 页上的订购信息。

VCCA. 模拟系统内核调压器的输出引脚或模拟系统内核的输入 引脚。需要为 VSSA 连接 1 μF 电容。电压调节器输出不适用于 驱动外部电路。注意,如果您使用具有外部内核电压调节器的器 件(外部调制模式),供给该引脚的电压不能超过允许范围(1.71 V 至 1.89 V)。使用内部内核电压调节器 (内部调制模式,即默 认模式)时,不要供电给该引脚。有关详细信息,请参见第 30 页 上的供电系统。

VCCD. 数字系统内核电压调节器的输出引脚或数字系统内核的输入引脚。两个 VCCD 引脚必须连接在一起,引脚之间的线路越短越好,并将 1 μF 电容连接到 VSSD。电压调节器输出不适用于驱动外部电路。注意,如果您使用具有外部内核电压调节器的器件(外部调制模式),供给该引脚的电压不能超过允许范围(1.71 V 至 1.89 V)。使用内部内核电压调节器 (内部调制模式,即默认模式)时,不要供电给该引脚。有关详细信息,请参见第 30 页上的供电系统。

VDDA. 所有模拟外设和模拟系统内核电压调节器的供电引脚。 VDDA 必须是器件上的最高电压。所有其他供电引脚必须小于或 等于 VDDA。

**VDDD.** 所有数字外设和数字系统内核电压调节器的供电引脚。 VDDD 必须小于或等于 **VDDA**。

VSSA. 所有模拟外设的接地引脚。

VSSB. 升压器的接地引脚。

VSSD. 所有数字逻辑和 I/O 引脚的接地引脚。

VDDIO0、VDDIO1、VDDIO2、VDDIO3. I/O 引脚的供电引脚。有关特定 I/O 引脚至 VDDIO 的映射,请参见引脚分布。每个VDDIO 都必须连接到有效的工作电压(1.71 V 至 5.5 V),并且必须小于或等于 VDDA。

XRES (与可配置的 XRES).外部复位引脚。内部上拉,低电平有效。可将引脚 P1[2] 配置为一个 XRES 引脚;请参见第 23 页上的非易失性锁存器 (NVL)。

# 4. CPU

# 4.1 8051 CPU

CY8C36器件采用与原来MCS-51指令集完全兼容的单周期8051 CPU。CY8C36 系列采用流水线 RISC 架构,在执行大多数指令时都能在1到2个周期内完成,能够提供高达33 MIPS 的峰值性能,并且每个指令平均需要两个周期。单周期8051 CPU的运行速度比标准8051 处理器快十倍。

8051 CPU 子系统包括下列特性:

- 单周期 8051 CPU

- 高达 64 KB 的闪存存储器,高达 2 KB 的 EEPROM,以及高达 8 KB 的 SRAM

- CPU 与闪存之间的 512 字节指令缓存

- ■可编程的嵌套向量中断控制器

- DMA 控制器

- ■外设集线器 (PHUB)

- ■外部存储器接口 (EMIF)

# 4.2 寻址模式

8051 支持下列寻址模式:

- 直接寻址: 通过8位直接地址字段指定操作数。使用此模式只能 访问内部 RAM 和 SFR。

- ■间接寻址:通过指令指定包含操作数地址的寄存器。寄存器 R0 或 R1 用于指定 8 位地址,数据指针 (DPTR)寄存器用于指定 16 位地址。

- 寄存器寻址:通过特定指令访问指定寄存器组中的其中一个寄存器(R0至R7)。这些指令无需地址字段,因此更为有效。

- 寄存器专用指令:有些指令是特定寄存器的专用指令。例如,有些指令始终在累加器中执行。在这种情况下,无需指定操作数。

- 立即常量: 有些指令直接使用常量值,而不是地址。

- ■索引寻址:此类寻址只能用于读取程序存储器。该模式采用数据指针作为基址,并采用累加器的值作为偏移量,来读取程序存储器。

- ■位寻址:在此模式下,操作数是256位中的其中一位。

# 4.3 指令集

8051 指令集已经过高度优化,能够进行 8 位处理和 Boolean 运算。支持的指令类型包括:

- ■算术指令

- ■逻辑指令

- ■数据传输指令

- Boolean 指令

- ■程序分支指令

# 4.3.1 指令集摘要 4.3.1.1 算术指令

算术指令支持以下寻址模式:直接寻址、间接寻址、寄存器寻址、 立即常量寻址和寄存器专用指令寻址。算术模式用于执行加、 减、乘、除、递增和递减运算。第 14 页上的表 4-1 列出了不同 的算术指令。

# 表 4-1. 算术指令

| 助记符           | 说明                    | 字节 | 周期 |

|---------------|-----------------------|----|----|

| ADD A,Rn      | 将寄存器的值加到累加器           | 1  | 1  |

| ADD A,Direct  | 将直接访问字节的值加到累加器        | 2  | 2  |

| ADD A,@Ri     | 将间接访问 RAM 的数据加到累加器    | 1  | 2  |

| ADD A,#data   | 将立即数加到累加器             | 2  | 2  |

| ADDC A,Rn     | 将寄存器值带进位加到累加器         | 1  | 1  |

| ADDC A,Direct | 将直接访问字节的值带进位加到累加器     | 2  | 2  |

| ADDC A,@Ri    | 将间接访问 RAM 的数据带进位加到累加器 | 1  | 2  |

| ADDC A,#data  | 将立即数带进位加到累加器          | 2  | 2  |

| SUBB A,Rn     | 从累加器带借位减去寄存器值         | 1  | 1  |

| SUBB A,Direct | 从累加器带借位减去直接访问字节       | 2  | 2  |

| SUBB A,@Ri    | 从累加器带借位减去 RAM 内的间接值   | 1  | 2  |

| SUBB A,#data  | 从累加器带借位减去立即数          | 2  | 2  |

| INC A         | 累加器值加 1               | 1  | 1  |

| INC Rn        | 寄存器值加 1               | 1  | 2  |

| INC Direct    | 直接访问字节加 1             | 2  | 3  |

| INC @Ri       | RAM 内的间接值加 1          | 1  | 3  |

| DEC A         | 累加器的值减 1              | 1  | 1  |

| DEC Rn        | 寄存器值减 1               | 1  | 2  |

| DEC Direct    | 直接访问字节的值减 1           | 2  | 3  |

| DEC @Ri       | RAM 内的间接值减 1          | 1  | 3  |

| INC DPTR      | 数据指针加 1               | 1  | 1  |

| MUL           | 累加器的值乘以 B             | 1  | 2  |

| DIV           | 累加器的值除以 B             | 1  | 6  |

| DAA           | 对累加器的值进行十进制调整         | 1  | 3  |

# 4.3.1.2 逻辑指令

逻辑指令用于对字节执行 AND、OR、XOR 等 Boolean 运算,对累加器的内容执行循环移位,以及交换累加器中的半字节。针对字节的 Boolean 运算是按位执行的。第 14 页上的表 4-2 列出了逻辑指令及其说明。

表 4-2. 逻辑指令

|     | 助记符           | 说明                         | 字节 | 周期 |

|-----|---------------|----------------------------|----|----|

| ANL | A,Rn          | 累加器与寄存器相 " 与 " (AND)       | 1  | 1  |

| ANL | A,Direct      | 累加器与直接访问字节相 " 与 " (AND)    | 2  | 2  |

| ANL | A,@Ri         | 累加器与 RAM 内的间接值相 "与(AND)    | 1  | 2  |

| ANL | A,#data       | 累加器与立即数相 " 与 " (AND)       | 2  | 2  |

| ANL | Direct, A     | 直接访问字节与累加器相 " 与 " (AND)    | 2  | 3  |

| ANL | Direct, #data | 直接访问字节与立即数相 " 与 " (AND)    | 3  | 3  |

| ORL | A,Rn          | 累加器与寄存器相"或"(OR)            | 1  | 1  |

| ORL | A,Direct      | 累加器与直接访问字节相 " 或 " (OR)     | 2  | 2  |

| ORL | A,@Ri         | 累加器与 RAM 内的间接值相 " 或 " (OR) | 1  | 2  |

| ORL | A,#data       | 累加器与立即数相 " 或 " (OR)        | 2  | 2  |

文档编号: 001-92989 版本\*A 页 14/130

# 表 4-2. 逻辑指令 (续)

|      | 助记符           | 说明                         | 字节 | 周期 |

|------|---------------|----------------------------|----|----|

| ORL  | Direct, A     | 直接访问字节与累加器相 " 或 " (OR)     | 2  | 3  |

| ORL  | Direct, #data | 直接访问字节与立即数相 " 或 " (OR)     | 3  | 3  |

| XRL  | A,Rn          | 累加器与寄存器相 " 异或 " (XOR)      | 1  | 1  |

| XRL  | A,Direct      | 累加器与直接访问字节相 " 异或 " (XOR)   | 2  | 2  |

| XRL  | A,@Ri         | 累加器与 RAM 内的间接值相 "异或" (XOR) | 1  | 2  |

| XRL  | A,#data       | 累加器与立即数相 " 异或 " (XOR)      | 2  | 2  |

| XRL  | Direct, A     | 直接访问字节与累加器相 " 异或 " (XOR)   | 2  | 3  |

| XRL  | Direct, #data | 直接访问字节与立即数相 " 异或 " (XOR)   | 3  | 3  |

| CLR  | Α             | 累加器清零                      | 1  | 1  |

| CPL  | Α             | 实现累加器的补码                   | 1  | 1  |

| RL   | Α             | 累加器循环左移                    | 1  | 1  |

| RLC  | Α             | 累加器带进位循环左移                 | 1  | 1  |

| RR   | Α             | 累加器循环右移                    | 1  | 1  |

| RRC  | A             | 累加器带进位循环右移                 | 1  | 1  |

| SWAF | PA            | 交换累加器中的半字节                 | 1  | 1  |

# 4.3.1.3 数据传输指令

数据传输指令有三种类型:内核 RAM、外部数据 RAM 以及查询表。内核 RAM 传输包括任意两个内核 RAM 地址或 SFR 之间的传输。这些指令可以采用直接寻址、间接寻址、寄存器寻址和立即寻址模式。外部数据 RAM 传输仅包括累加器和外部数据 RAM 地址之间的传输。它只能采用间接寻址模式。除了使用索引寻址模式读取程序存储器之外,查询表不涉及任何其他内容。表 4-3 列出了各种可用数据传输指令。

# 4.3.1.4 Boolean 指令

8051 内核具有一个单独的位寻址存储器地址,其中包括 128 位的位寻址RAM以及一组位寻址SFR。指令集包括所有的位运算,如传输、置位、清零、求反、或(OR)、与(AND)指令,以及条件跳转指令。第16页上的表4-4列出了可用的Boolean指令。

# 表 4-3. 数据传输指令

|     | 助记符            | 说明                      | 字节 | 周期 |

|-----|----------------|-------------------------|----|----|

| MOV | A,Rn           | 将寄存器的值传输到累加器中           | 1  | 1  |

| MOV | A,Direct       | 将直接访问字节传输到累加器中          | 2  | 2  |

| MOV | A,@Ri          | 将间接访问 RAM 的数据传输到累加器中    | 1  | 2  |

| MOV | A,#data        | 将立即数传输到累加器中             | 2  | 2  |

| MOV | Rn,A           | 将累加器的值传输到寄存器中           | 1  | 1  |

| MOV | Rn,Direct      | 将直接访问字节传输到寄存器中          | 2  | 3  |

| MOV | Rn, #data      | 将立即数传输到寄存器中             | 2  | 2  |

| MOV | Direct, A      | 将累加器的值传输到直接访问字节         | 2  | 2  |

| MOV | Direct, Rn     | 将寄存器的值传输到直接访问字节中        | 2  | 2  |

| MOV | Direct, Direct | 将直接访问字节的值传输到直接访问字节中     | 3  | 3  |

| MOV | Direct, @Ri    | 将间接访问 RAM 的数据传输到直接访问字节中 | 2  | 3  |

| MOV | Direct, #data  | 将立即数传输到直接访问字节中          | 3  | 3  |

| MOV | @Ri, A         | 将累加器的数据传输到间接 RAM 中      | 1  | 2  |

| MOV | @Ri, Direct    | 将直接访问字节传输到间接 RAM 中      | 2  | 3  |

| MOV | @Ri, #data     | 将立即数传输到间接 RAM 中         | 2  | 2  |

| MOV | DPTR, #data16  | 将 16 位常量加载到数据指针的地址      | 3  | 3  |

文档编号: 001-92989 版本\*A 页 15/130

# 表 4-3. 数据传输指令 (续)

| 助记符             | 说明                     | 字节 | 周期 |

|-----------------|------------------------|----|----|

| MOVC A, @A+DPTR | 将相对于 DPTR 的代码字节传输到累加器中 | 1  | 5  |

| MOVC A, @A + PC | 将 PC 的代码字节传输到累加器       | 1  | 4  |

| MOVX A,@Ri      | 将外部 RAM (8位)的值传输到累加器   | 1  | 4  |

| MOVX A, @DPTR   | 将外部 RAM (8位)的值传输到累加器   | 1  | 3  |

| MOVX @Ri, A     | 将累加器的值传输到外部 RAM (8位)   | 1  | 5  |

| MOVX @DPTR, A   | 将累加器的值传输到外部 RAM (16 位) | 1  | 4  |

| PUSH Direct     | 将直接访问字节推入堆栈            | 2  | 3  |

| POP Direct      | 弹出堆栈中的直接访问字节           | 2  | 2  |

| XCH A, Rn       | 交换寄存器与累加器的值            | 1  | 2  |

| XCH A, Direct   | 交换直接访问字节与累加器的值         | 2  | 3  |

| XCH A, @Ri      | 交换间接 RAM 与累加器的值        | 1  | 3  |

| XCHD A, @Ri     | 交换低位间接数字 RAM 与累加器的值    | 1  | 3  |

# 表 4-4. 布尔指令

| 助记符          | 说明                     | 字节 | 周期 |

|--------------|------------------------|----|----|

| CLR C        | 进位清零                   | 1  | 1  |

| CLR bit      | 直接位清零                  | 2  | 3  |

| SETB C       | 设置进位                   | 1  | 1  |

| SETB bit     | 设置直接位                  | 2  | 3  |

| CPL C        | 实现进位的补码                | 1  | 1  |

| CPL bit      | 实现直接位的补码               | 2  | 3  |

| ANL C, bit   | 进位与直接位相 " 与 " (AND)    | 2  | 2  |

| ANL C, /bit  | 进位与直接位的补码相 " 与 " (AND) | 2  | 2  |

| ORL C, bit   | 进位与直接位相"或(OR)"         | 2  | 2  |

| ORL C, /bit  | 进位与直接位的补码相 " 或 " (OR)  | 2  | 2  |

| MOV C, bit   | 将直接位传输到进位              | 2  | 2  |

| MOV bit, C   | 将进位传输到直接位              | 2  | 3  |

| JC rel       | 如果置位了进位,则跳转            | 2  | 3  |

| JNC rel      | 如果未置位进位,则跳转            | 2  | 3  |

| JB bit, rel  | 如果置位了直接位,则跳转           | 3  | 5  |

| JNB bit, rel | 如果未置位直接位,则跳转           | 3  | 5  |

| JBC bit, rel | 如果置位了直接位,则跳转,并使该位清零    | 3  | 5  |

# 4.3.1.5 程序分支指令

8051 支持一组条件和无条件跳转指令,用于帮助修改程序执行流程。表 4-5 列出了这些跳转指令。

# 表 4-5. 跳转指令

| 助记符                  | 说明                       | 字节 | 周期 |

|----------------------|--------------------------|----|----|

| ACALL addr11         | 绝对调用子程序                  | 2  | 4  |

| LCALL addr16         | 长调用子程序                   | 3  | 4  |

| RET                  | 从子程序返回                   | 1  | 4  |

| RETI                 | 从中断返回                    | 1  | 4  |

| AJMP addr11          | 绝对跳转                     | 2  | 3  |

| LJMP addr16          | 长跳转                      | 3  | 4  |

| SJMP rel             | 短跳转 (相对地址)               | 2  | 3  |

| JMP @A + DPTR        | 相对于 DPTR 间接跳转            | 1  | 5  |

| JZ rel               | 如果累加器值为零,则跳转             | 2  | 4  |

| JNZ rel              | 如果累加器值不为零,则跳转            | 2  | 4  |

| CJNE A,Direct, rel   | 直接访问字节与累加器进行比较,如果不相等则跳转  | 3  | 5  |

| CJNE A, #data, rel   | 比较立即数与累加器,不相等则跳转         | 3  | 4  |

| CJNE Rn, #data, rel  | 比较立即数与寄存器,不相等则跳转         | 3  | 4  |

| CJNE @Ri, #data, rel | 比较立即数与间接访问 RAM 的值,不相等则跳转 | 3  | 5  |

| DJNZ Rn,rel          | 寄存器值减 1, 结果不为零则跳转        | 2  | 4  |

| DJNZ Direct, rel     | 直接访问字节减 1, 结果不为零则跳转      | 3  | 5  |

| NOP                  | 无操作                      | 1  | 1  |

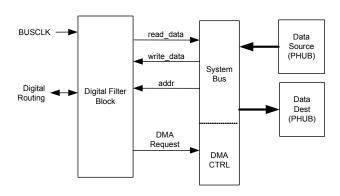

# 4.4 DMA与PHUB

PHUB 和 DMA 控制器负责 CPU 和外设之间的数据传输,以及外设之间的数据传输,此外还控制引导期间的器件配置。PHUB 包括:

- ■一个中央集线器,其中包括 DMA 控制器、仲裁器和路由器

- ■从集线器向外辐射到大多数外设的多个并行访问路径

有两个 PHUB 主设备: 即 CPU 和 DMA 控制器。这两个主设备都可以启动总线上的数据操作。DMA 通道可以处理外设通信,而无需 CPU 干预。如果有多个请求,中央集线器中的仲裁器将决定哪个 DMA 通道具有最高优先级。

# 4.4.1 PHUB 特性

- CPU 与 DMA 控制器都是 PHUB 的总线主设备

- ■八个多层 AHB 总线并行访问路径,用于外设访问

- ■对位于不同并行访问路径上的外设进行同步 CPU 和 DMA 访问

- 在不同并行访问路径上进行同步DMA源和目的地突发(Burst)数据操作

- 支持 8、16、24 和 32 位寻址和数据

表 4-6. PHUB 多层并行访问路径 (Spoke) 和外设

| PHUB 多层<br>并行访问路径 | 外设                                            |

|-------------------|-----------------------------------------------|

| 0                 | SRAM                                          |

| 1                 | IO、PICU、EMIF                                  |

| 2                 | PHUB 局部配置、电源管理器、时钟、 IC、<br>SWV、 EEPROM、闪存编程接口 |

| 3                 | 模拟接口与 Trim, 抽取滤波器                             |

| 4                 | USB、CAN、I <sup>2</sup> C、定时器、计数器和 PWM         |

| 5                 | DFB                                           |

| 6                 | UDB 组 1                                       |

| 7                 | UDB 组 2                                       |

# 4.4.2 DMA 特性

- 24 个 DMA 通道

- 每个通道有一个或多个数据操作描述符(TD),以便配置通道行为。总共可以定义多达 128 个 TD

- 可动态更新 TD

- ■每个通道具有八个优先级别

- ■任何数字路由信号、CPU 或其他 DMA 通道均可触发数据操作

- ■每个通道在每次传输时最多可以生成两个中断

- ■可以停止或取消数据操作

- 支持任意大小 (即 1 至 64 KB)的数据操作

- ■可以嵌套和/或链接 TD,以进行复杂的数据操作

# 4.4.3 优先级别

当 CPU 访问和 DMA 控制器访问需要相同的总线资源时, CPU 的优先级始终高于 DMA 控制器。不过,所采用的系统架构决定了 CPU 永远都不会独占资源,而让 DMA 一直等待。具有较高优先级(优先级编号较小)的 DMA 通道可以中断当前的 DMA 传输。在这种情况下,系统会允许当前传输完成其当前数据操作。当多个 DMA 访问请求同时发生时,为了确保延迟限制,公平算法会在优先级别 2 至 7 之间进行调度,以确保最低总线带宽的交错百分比。优先级别 0 和 1 不会参与公平算法,并且可以使用100% 的总线带宽。如果具有相同优先级别的两个 DMA 请求同时发生,则会使用简单的轮循算法来平等地使用所分配的带宽。可以针对每个 DMA 通道禁用轮循分配,以便使相应通道始终位于队列的开头。在满足了 CPU 和 DMA 优先级别 0 和 1 的要求之后,系统会保证优先级别 2 至 7 可以分配到表 4-7 中所示的最低总线带宽。

### 表 4-7. 优先级

| 优先级 | 总线带宽百分比 |

|-----|---------|

| 0   | 100.0   |

| 1   | 100.0   |

| 2   | 50.0    |

| 3   | 25.0    |

| 4   | 12.5    |

| 5   | 6.2     |

| 6   | 3.1     |

| 7   | 1.5     |

如果禁用公平算法,则仅根据优先级别为 DMA 访问分配资源;而不会提供任何总线带宽保障。

# 4.4.4 支持的数据操作模式

由于可以灵活地配置每个 DMA 通道并能够链接多个通道,因此既可以创建简单的用例,也可以创建复杂的用例。一般用例包括(但不限于):

# 4.4.4.1 简单 DMA

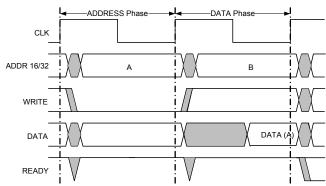

在简单 DMA 中,使用单个 TD 在来源和接收器 (外设或存储器位置)之间传输数据。 DMA 读 / 写周期的基本时序图,如图 4-1 所示。有关其他传输模式的更多说明,请参考技术参考手册。

# 图 4-1. DMA 时序图

Basic DMA Read Transfer without wait states

# ADDRESS Phase DATA Phase CLK ADDR 16/32 A B WRITE DATA DATA A DATA READY

Basic DMA Write Transfer without wait states

### 4.4.4.2 自动重复 DMA

当从系统存储器重复读取静态样本,并将其写入到外设中时,通常会使用自动重复DMA。重复操作是通过与其自身相链接的单个TD来实现的。

# 4.4.4.3 交替 DMA

通过采用双缓冲技术,交替 DMA 允许一个客户在向一个缓冲区存入数据的同时,另一个客户使用另一个缓冲区中先前收到的数据。在最简单的情况下,这可以通过以下方法来实现:将两个 TD 链接在一起,以便每个 TD 在完成后调用另一个 TD。

# 4.4.4.4 循环 DMA

循环 DMA 与交替 DMA 类似,只不过它包含两个以上的缓冲区。这种用例包含多个TD;最后一个TD完成后会链回到第一个TD。

# 4.4.4.5 分散/聚集 DMA

在分散 / 聚集 DMA 中,需要有多个非连续的来源或目的地,以便有效地执行整个 DMA 数据操作。例如,可能需要将某个数据包发送到器件之外,而该数据包的各个元素(包括包头、包体和包尾)位于存储器中不同的非连续位置。分散 / 聚集 DMA 允许使用链中的多个 TD 将各个段连接在一起。链会聚集多个位置中的数据。类似概念也适用于在器件上接收数据。在收到的数据中,某些部分可能需要分散到存储器中的不同位置,以便软件进行处理。链中的每个 TD 用于指定链中每个离散元素的位置。

# 4.4.4.6 数据包排队 DMA

数据包排队 DMA 与分散 / 聚集 DMA 类似,但明确引用数据包协议。借助这些协议,发送或接收数据包可以采用单独的配置、数据和状态阶段。

例如,要发送数据包,可以将存储器映射配置寄存器的内容写入到外设中,并指定后续数据阶段的总长度。CPU 可以在系统存储器中的任意位置设置此配置信息,并将其与简单 TD 一起复制到外设。配置阶段结束后,即可开始一个或一系列数据阶段 TD (可能会使用分散 / 聚集)。数据阶段 TD 结束后,可以调用状态阶段 TD,以便从外设读取某些存储器映射状态信息,并将其复制到CPU 指定的系统存储器中的某个位置,以便稍后进行检查。可以将多组配置、数据和状态阶段" 子链" 连成一条更长的链,以便按此方式传送多个数据包。反向接收数据包采用了类似概念。

# 4.4.4.7 嵌套 DMA

一个 TD 可以修改另一个 TD, 因为与任何其他外设一样, TD 配置空间也已进行存储器映射。例如,第一个 TD 加载第二个 TD 的配置,然后调用第二个 TD。第二个 TD 按应用要求传输数据。完成后,第二个 TD 调用第一个 TD,第一个 TD 再次更新第二个 TD 的配置。该过程可以根据需要重复任意多次。

# 4.5 中断控制器

借助中断控制器,硬件资源可以独立于主代码正在执行的当前任务,使程序执行流程跳转到新的地址处。该中断控制器具备原来的 8051 中断控制器所不具备的增强功能:

- ■32 个中断向量

- 直接跳转到代码空间中具有动态向量地址的 ISR 任意位置

- ■每个向量有多个源可供选择

- 灵活中断,以执行向量匹配

- ■能够独立使能或禁用每个中断向量

- ■可以为每个中断动态指定八个优先级中的其中一个优先级

- ■八级嵌套中断

- 多个 I/O 中断向量

- 软件可以发送中断

- ■软件可以清除待处理中断

当有待处理中断时,当前指令完成后,程序计数器的内容会被推入到堆栈中。然后,代码执行流程会跳转到向量提供的程序地址处。在 ISR 完成后,会执行 RETI 指令,以便返回到先前被中断指令之后的下一条指令处。为此, RETI 指令会从堆栈中弹出程序计数器的内容。

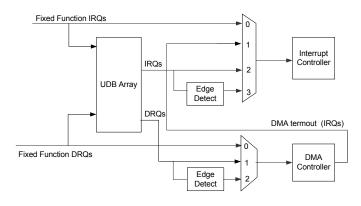

如果为两个或多个中断指定了相同的优先级别,则首先执行向量编号较低的中断。每个中断向量有三个中断源可供选择,即:固定函数、DMA以及UDB。固定函数中断是直接连接到最常见的中断源,这种连接的资源成本最低。如果使用DMA中断源,则直接连接到每个DMA通道所提供的两个DMA中断源。第三个向量中断源来自UDB数字路由阵列。在这种情况下,UDB阵列可用的任意数字信号都可用作中断源。通过使用UDB中断源连接,固定函数中断和所有中断源可以连接至任意中断向量。

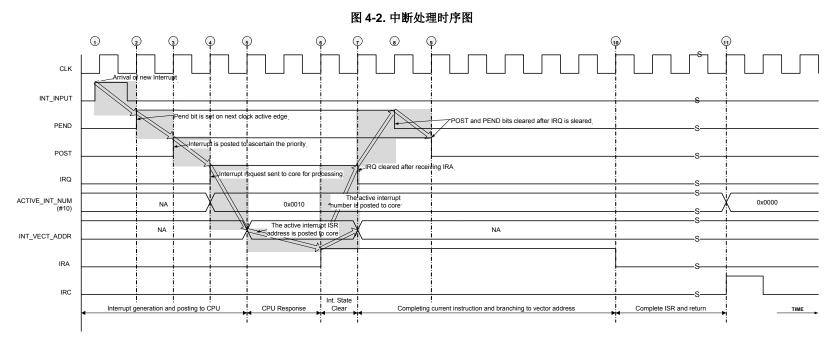

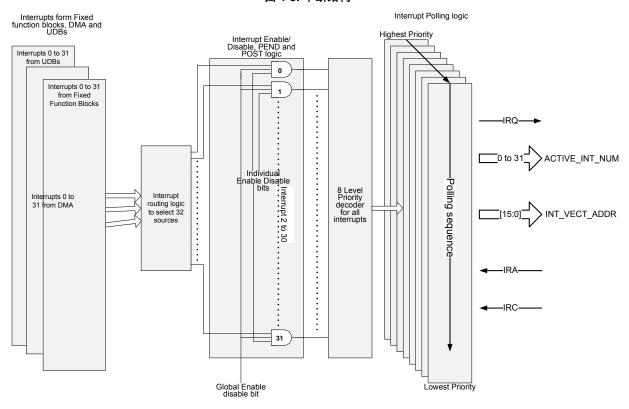

第 20 页上的图 4-2 代表中断触发时的典型事件流。第 21 页上的图 4-3 显示了中断结构和优先级轮询。

# 注意:

- 1: 触发的中断与时钟异步

- 2: PEND 位将在下一活跃时钟沿进行设置,以指示中断到达

- 3: POST 位将在 PEND 位之后进行设置

- 4: 中断请求和中断编号将在评估优先级之后发往 CPU 内核 (需要 3 个时钟循环次数)

- 5: ISR 地址被发送到 CPU 内核用于分支

- 6: CPU 应答中断请求

- 7: ISR 被 CPU 读取用于分支

- 8、9: 从内核收到 IRA 之后, PEND 和 POST 位将分别清除

- 10: 完成当前指令并开始从 ISR 位置执行指令之后清除 IRA 位 (需要 7 个时钟循环次数)

- 11: 设置 IRC 表明 ISR 完成,活跃中断状态被恢复成先前的状态

- 中断的总延迟 (ISR 执行)

- = POST + PEND + IRQ + IRA + 完成当前指令及分支

- = 1+1+1+2+7 周期

- = 12 个周期

文档编号: 001-92989 版本 \*A 页 20/130

# 图 4-3. 中断结构

表 4-8. 中断向量表

| 序号 | 固定功能             | DMA               | UDB          |

|----|------------------|-------------------|--------------|

| 0  | LVD              | phub_termout0[0]  | udb_intr[0]  |

| 1  | 缓存 /ECC          | phub_termout0[1]  | udb_intr[1]  |

| 2  | 预留               | phub_termout0[2]  | udb_intr[2]  |

| 3  | 睡眠 (电源管理)        | phub_termout0[3]  | udb_intr[3]  |

| 4  | PICU[0]          | phub_termout0[4]  | udb_intr[4]  |

| 5  | PICU[1]          | phub_termout0[5]  | udb_intr[5]  |

| 6  | PICU[2]          | phub_termout0[6]  | udb_intr[6]  |

| 7  | PICU[3]          | phub_termout0[7]  | udb_intr[7]  |

| 8  | PICU[4]          | phub_termout0[8]  | udb_intr[8]  |

| 9  | PICU[5]          | phub_termout0[9]  | udb_intr[9]  |

| 10 | PICU[6]          | phub_termout0[10] | udb_intr[10] |

| 11 | PICU[12]         | phub_termout0[11] | udb_intr[11] |

| 12 | PICU[15]         | phub_termout0[12] | udb_intr[12] |

| 13 | 比较器共用            | phub_termout0[13] | udb_intr[13] |

| 14 | 开关电容共用           | phub_termout0[14] | udb_intr[14] |

| 15 | I <sup>2</sup> C | phub_termout0[15] | udb_intr[15] |

| 16 | CAN              | phub_termout1[0]  | udb_intr[16] |

| 17 | 定时器/计数器0         | phub_termout1[1]  | udb_intr[17] |

| 18 | 定时器/计数器1         | phub_termout1[2]  | udb_intr[18] |

| 19 | 定时器/计数器2         | phub_termout1[3]  | udb_intr[19] |

| 20 | 定时器/计数器3         | phub_termout1[4]  | udb_intr[20] |

| 21 | USB SOF 中断       | phub_termout1[5]  | udb_intr[21] |

| 22 | USB 仲裁器中断        | phub_termout1[6]  | udb_intr[22] |

# 表 4-8. 中断向量表 (续)

| 序号 | 固定功能            | DMA               | UDB          |

|----|-----------------|-------------------|--------------|

| 23 | USB 总线中断        | phub_termout1[7]  | udb_intr[23] |

| 24 | USB Endpoint[0] | phub_termout1[8]  | udb_intr[24] |

| 25 | USB 端点数据        | phub_termout1[9]  | udb_intr[25] |

| 26 | 预留              | phub_termout1[10] | udb_intr[26] |

| 27 | LCD             | phub_termout1[11] | udb_intr[27] |

| 28 | DFB Int         | phub_termout1[12] | udb_intr[28] |

| 29 | 抽取滤波器中断         | phub_termout1[13] | udb_intr[29] |

| 30 | PHUB 错误中断       | phub_termout1[14] | udb_intr[30] |

| 31 | EEPROM 故障中断     | phub_termout1[15] | udb_intr[31] |

# 5. 存储器

# 5.1 静态 RAM

CY8C36 静态 RAM(SRAM)用于临时存储数据。提供了高达 8 KB 的 SRAM,该 SRAM 能够通过 8051 或 DMA 控制器进行访问。请参见第 25 页上的存储器映射。 8051 和 DMA 控制器可以同时访问 SRAM(前提是访问不同的 4 KB 模块)。

# 5.2 闪存程序存储器

PSoC 器件中的闪存旨在为用户固件、用户配置数据、批量数据存储和可选 ECC 数据提供非易失性存储空间。主闪存区包含多达 64 KB 的用户程序存储空间。

此外,还有高达 8 KB 的闪存空间用于存储纠错码 (ECC)。如果未使用 ECC,则此空间可以存储器件配置数据和批量用户数据。用户代码可能无法用完 ECC 闪存存储空间。ECC 能够以固件存储器的每 8 个字节为一个单位,来纠正一位错误并检测两位错误;如果检测到错误,则会生成中断。

CPU通过缓存控制器读取位于闪存中的指令。这样能够提高指令的执行速度,并且因降低了闪存访问的频率而可以减少系统功耗。缓存包括 8 行,每行包含 64 个字节,总共有 512 个字节。它可以完全与其他组件结合,并自动控制闪存功耗,以及可以被使能或禁用。如果使能 ECC,缓存控制器也会执行错误检查和校正,以及生成中断。

闪存编程通过专用接口来执行,在此期间不允许在闪存之内执行代码。闪存编程接口会执行闪存擦除、编程,并设置代码保护级别。闪存系统内串行编程(ISSP)通常用于生产编程,可通过SWD和 JTAG 接口来实现。系统内编程通常用于 Bootloaders,也可以通过 I<sup>2</sup>C、USB、UART、SPI 等串行接口或任何通信协议来实现。

# 5.3 闪存安全性

所有 PSoC 器件均包括灵活的闪存保护模型,以防止访问和查看片上闪存,从而防止对专有代码进行复制或逆向工程设计。闪存划分为若干个模块,其中每个模块都包含 256 个字节的程序或数据以及 32 个字节的 ECC 或配置数据。64 KB 的闪存器件总共提供多达 256 个模块。

器件允许用户为闪存的每一行指定四个保护级别中的其中一个。表 5-1 列出了可用的保护模式。要更改闪存保护级别,必须擦除整个闪存。完全保护和现场升级保护设置旨在禁用外部访问(例如,通过 PSoC Creator 等调试工具)。如果应用程序需要通过Bootloader 进行代码更新,请使用现场升级保护设置。仅当应用程序没有任何安全性方面的要求时,才能使用无保护设置。PSoC 提供名为器件安全的高级功能。通过该功能可以永久禁用所有测试、编程和调试端口,从而阻止应用程序的外部访问(请参见第 66 页上的器件安全性)。有关如何充分利用 PSoC 安全性功能的详细信息,请参见 PSoC 3 TRM。

# 表 5-1. 闪存保护

| 保护设置 | 支持                  | 不支持               |

|------|---------------------|-------------------|

| 无保护  | 外部读写访问 + 内部读<br>写访问 | -                 |

| 工厂升级 | 外部写访问 + 内部读写<br>访问  | 外部读访问             |

| 现场升级 | 内部读写访问              | 外部读写访问            |

| 完全保护 | 内部读访问               | 外部读写访问 +<br>内部写访问 |

# 免责声明

请注意以下与赛普拉斯器件上的闪存代码保护功能有关的详细信息。

赛普拉斯产品符合相应的赛普拉斯数据手册中所包含的规范。塞普拉斯坚信,不论如何使用,其产品系列的安全性在目前市场上的同类产品中始终名列前矛。目前可能存在一些赛普拉斯不了解的,能够破坏代码保护功能的方法。据我们所知,任何此类方法都是不正当的,并且可能是违法的。不只是赛普拉斯,任何其他半导体制造商都无法保证各自代码的安全性。代码保护并非意味着我们保证产品"坚不可推"。

赛普拉斯非常希望能够与关注其代码完整性的客户通力合作。代码保护技术正在不断发展。持续改进产品的代码保护功能是赛普拉斯的不懈追求。

# 5.4 EEPROM

PSoC EEPROM 存储器是一种按字节寻址的非易失性存储器。CY8C36 提供了高达 2 KB 的 EEPROM 存储器来存储用户数据。对 EEPROM 的读访问是按字节进行的随机访问。读访问直接进行;写访问则通过向 EEPROM 编程接口发送写指令来进行。在 EEPROM 写访问期间,可以继续从闪存执行 CPU 代码。EEPROM 的擦除和写操作是以行为单位进行的。EEPROM 共有 128 行,每行有 16 个字节。所有 EEPROM 字节的出厂默认值均为 0。

因为 EEPROM 将被映射到 8051 外部空间中, 所以 CPU 不能在 EEPROM 空间内执行代码。没有任何 ECC 硬件与 EEPROM 相关联。如果需要 ECC, 必须在固件中对其进行处理。

写入 EEPROM 或闪存可能需要 20 毫秒的时间。在这个时间内不能复位器件,否则将导致 EEPROM 或闪存的意外更改。复位源 (请参见 第 6.3.1 节) 包括 XRES 引脚、软件复位以及看门狗; 需要确保这些源不被无意激活。另外,低电压检测线路可以配置为生成中断而不是复位。

# 5.5 非易失性锁存器 (NVL)

PSoC 具有一个 4 字节、用于复位时配置设备的非易失性锁存器 (NVL) 阵列。 NVL 寄存器映射如表 5-2 所示。

# 表 5-2. 设备配置 NVL 寄存器映射

| 寄存器地址 | 7                | 6            | 5        | 4            | 3            | 2            | 1            | 0            |  |

|-------|------------------|--------------|----------|--------------|--------------|--------------|--------------|--------------|--|

| 0x00  | PRT3RE           | PRT3RDM[1:0] |          | PRT2RDM[1:0] |              | PRT1RDM[1:0] |              | PRT0RDM[1:0] |  |

| 0x01  | PRT12RDM[1:0]    |              | PRT6R    | DM[1:0]      | PRT5RDM[1:0] |              | PRT4RDM[1:0] |              |  |

| 0x02  | XRESMEN          | DBGEN        | :N       |              |              |              | PRT1         | 5RDM[1:0]    |  |

| 0x03  | DIG_PHS_DLY[3:0] |              | DLY[3:0] |              | ECCEN        | DPS          | [1:0]        | CFGSPEED     |  |

有关各个字段的详细信息及其出厂默认设置如表 5-3 所示。

# 表 5-3. 字段和出厂默认设置

| 字段               | 说明                                                        | 设置                                                               |

|------------------|-----------------------------------------------------------|------------------------------------------------------------------|

| PRTxRDM[1:0]     | 用于控制相应 IO 端口的复位驱动模式。请参见第 41 页上的复位配置。端口的所有引脚都设为相同模式。       | 00b (默认) — 模拟高阻抗<br>01b — 数字高阻抗<br>10b — 电阻上拉<br>11b — 电阻下拉      |

| XRESMEN          | 用于控制引脚 P1[2] 被用作 GPIO 还是外部复位。请参见第 12 页上的引脚说明以便了解 XRES 说明。 | 0 (68 引脚和 100 引脚器件的默认设置) — GPIO 1 (48 引脚器件的默认设置) — 外部复位          |

| DBGEN            | 调试使能,允许访问调试系统,用于第三方编程器。                                   | 0 — 访问禁止<br>1 (默认值) — 访问使能                                       |

| CFGSPEED         | 在器件启动过程中控制基于 IMO 的时钟的速度,以加快启动或实现低功耗运行                     | 0(默认值)— 12 MHz IMO<br>1 — 48 MHz IMO                             |

| DPS{1:0]         | 用于控制多个用作调试端口 P1 引脚的使用情况。请参见第 63 页上的编程、调试接口与资源。            | 00b — 5 线 JTAG<br>01b(默认)— 4 线 JTAG<br>10b — SWD<br>11b — 调试端口禁用 |

| ECCEN            | 控制ECC闪存是用于ECC还是用于常规配置和数据存储。请参见第 22 页上的闪存程序存储器。            | 0 — ECC 禁用<br>1 (默认) — ECC 使能                                    |

| DIG_PHS_DLY[3:0] | 选择数字时钟相位延迟。                                               | 有关详细信息,请参见 TRM。                                                  |

虽然 PSoC Creator 为修改设备配置 NVL 提供了支持,但 NVL 擦 / 写循环的次数仍然有限 — 请参见第 108 页上的非易失性锁存器 (NVL)。

# 5.6 外部存储器接口

CY8C36 提供一个外部存储器接口(EMIF),用于连接外部存储器。采用这种连接方式时,可以对外部存储器进行读写访问。EMIF 将与 UDB、I/O 端口以及其他硬件协同工作,以便生成外部存储器地址和控制信号。在频率为 33 MHz 时,每个存储器访问周期将需要四个总线时钟周期。

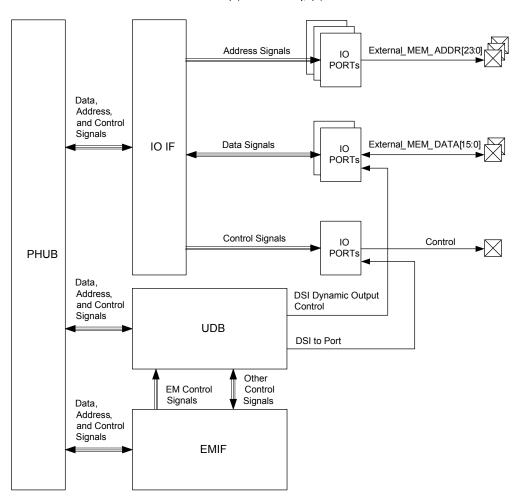

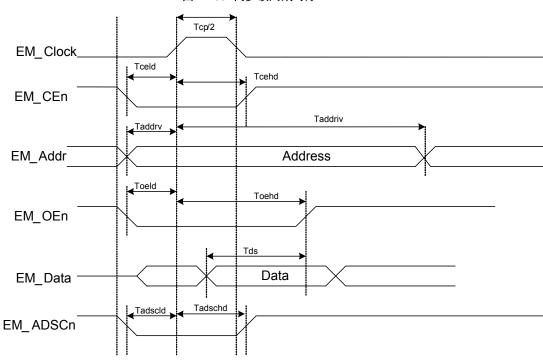

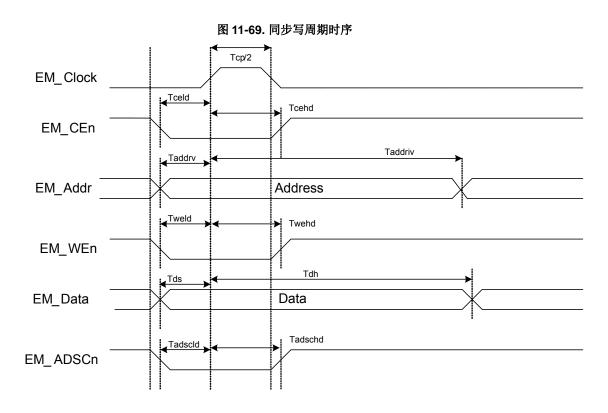

图 5-1 是 EMIF 框图。EMIF 支持同步和异步存储器。CY8C36 一次仅支持一种类型的外部存储器。

可以通过 8051 外部数据(xdata)空间来访问外部存储器;可以使用多达 24 个地址位。请参见第 26 页上的外部数据空间。该存储器的宽度可以是 8 位或 16 位。

图 5-1. EMIF 框图

# 5.7 存储器映射

CY8C36 8051 存储器映射与 MCS-51 存储器映射非常类似。

# 5.7.1 代码空间

CY8C36 8051 代码空间为 64 KB。该空间中仅包含主闪存。请参见第 22 页上的闪存程序存储器。

# 5.7.2 内部数据空间

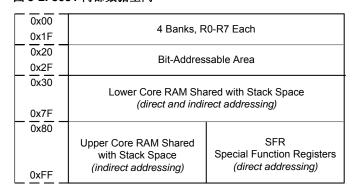

CY8C36 8051 内部数据空间为 384 个字节,压缩在 256 个字节的空间内。该空间包括 256 个字节的 RAM(除了第 22 页上的静态 RAM 中所述的 SRAM 之外)和用于特殊功能寄存器(SFR)的 128 个字节空间。请参见图 5-2。32 个最低位字节用于 4 组寄存器 R0-R7。接下来的 16 个字节是位寻址。

# 图 5-2.8051 内部数据空间

除了 48 个低位字节采用寄存器或位寻址模式之外,可以采用直接或间接寻址模式访问 128 个低位字节。采用直接寻址模式时,128 个高位字节会映射至 SFR。采用间接寻址模式时,128 个高位字节会映射至 RAM。堆栈操作采用间接寻址模式; 8051 堆栈空间为 256 个字节。请参见第 13 页上的寻址模式。

# 5.7.3 SFR

特殊功能寄存器 (SFR) 空间可让用户访问频繁访问的寄存器。表 5-4 显示了 SFR 存储器空间的存储器映射。

# 表 5-4. SFR 映射

| 地址   | 0/8        | 1/9        | 2/A         | 3/B  | 4/C  | 5/D  | 6/E | 7/F |

|------|------------|------------|-------------|------|------|------|-----|-----|

| 0×F8 | SFRPRT15DR | SFRPRT15PS | SFRPRT15SEL | _    | _    | _    | _   | _   |

| 0×F0 | В          | _          | SFRPRT12SEL | _    | _    | _    | _   | _   |

| 0×E8 | SFRPRT12DR | SFRPRT12PS | MXAX        | _    | _    | _    | _   | _   |

| 0×E0 | ACC        | _          | _           | _    | _    | _    | _   | _   |

| 0×D8 | SFRPRT6DR  | SFRPRT6PS  | SFRPRT6SEL  | _    | _    | _    | _   | _   |

| 0×D0 | PSW        | _          | _           | _    | _    | _    | _   | _   |

| 0×C8 | SFRPRT5DR  | SFRPRT5PS  | SFRPRT5SEL  | _    | _    | _    | _   | _   |

| 0×C0 | SFRPRT4DR  | SFRPRT4PS  | SFRPRT4SEL  | _    | _    | _    | _   | _   |

| 0×B8 | _          | _          | _           | _    | _    | _    | _   | _   |

| 0×B0 | SFRPRT3DR  | SFRPRT3PS  | SFRPRT3SEL  | _    | _    | _    | _   | _   |

| 0×A8 | IE         | _          | _           | _    | _    | _    | _   | _   |

| 0×A0 | P2AX       | _          | SFRPRT1SEL  | _    | _    | _    | _   | _   |

| 0×98 | SFRPRT2DR  | SFRPRT2PS  | SFRPRT2SEL  | _    | _    | _    | _   | _   |

| 0×90 | SFRPRT1DR  | SFRPRT1PS  | _           | DPX0 | _    | DPX1 | _   | _   |

| 0×88 | _          | SFRPRT0PS  | SFRPRT0SEL  | _    | _    | _    | _   | _   |

| 0×80 | SFRPRT0DR  | SP         | DPL0        | DPH0 | DPL1 | DPH1 | DPS | _   |

CY8C36 系列提供行业标准 8051 器件上使用的一组标准寄存器。此外, CY8C36 器件还添加了 SFR,以便直接访问器件上的 I/O 端口。以下章节对 CY8C36 系列中添加的 SFR 进行了介绍。

# 5.7.3.1 外部数据空间访问 SFR

8051 内核采用了双 DPTR 寄存器,能够更快地进行数据传输操作。数据指针选择 SFR (即 DPS) 用于选择下列指令所使用的数据指针寄存器 (DPTR0 或 DPTR1):

- MOVX @DPTR, A

- MOVX A, @DPTR

- MOVC A, @A+DPTR

- JMP @A+DPTR

- INC DPTR

- MOV DPTR, #data16

扩展数据指针 SFR(即 DPX0、DPX1、MXAX 和 P2AX)用于在访问外部数据空间期间,保留存储器地址的高位部分。这些 SFR 仅适用于 MOVX 指令。

在使用 DPTR0/DPTR1 寄存器执行 MOVX 指令期间,地址高位字节的内容始终等于 DPX0/DPX1 的内容。

在使用 R0 或 R1 寄存器执行 MOVX 指令期间,地址高位字节的 内容始终等于 MXAX 的内容,下一个高位字节的内容始终等于 P2AX 的内容。

### 5.7.3.2 I/O 端口 SFR

I/O 端口提供数字输入传感、输出驱动、引脚中断、模拟输入和输出连接、LCD、通过 DSI 访问外设等功能。有关 I/O 端口的完整信息,请参见第 35 页上的 I/O 系统与布线。

I/O 端口通过 PHUB 同 CPU 相连,并且还可以通过 SFR 访问。使用 SFR 能够更快地访问部分 I/O 端口寄存器,而使用 PHUB 则能够引导配置并访问所有 I/O 端口寄存器。

支持 SFR 的每个 I/O 端口都提供三个 SFR:

- SFRPRTxDR用于设置端口的输出数据状态(其中x为端口号,包括端口0至6、12和15)。

- SFRPRTxSEL 用于选择是由 PHUB PRTxDR 寄存器还是 SFRPRTxDR 控制端口内每个引脚的输出缓冲区。如果某个 SFRPRTxSEL[y] 位为高,则对应的 SFRPRTxDR[y] 位会设置 该引脚的输出状态。如果某个 SFRPRTxSEL[y] 位为低,则对应的 PRTxDR[y] 位会设置该引脚的输出状态(其中,y 介于 0 到 7 之间)。

- SFRPRTxPS 是包含端口引脚状态值的只读寄存器。

### 5.7.4 外部数据空间

8051 外部数据空间为 24 位,大小为 16 MB。该空间的绝大部分都不是 "外部"空间,而是供片上组件使用。请参见表 5-5。外部 (即片外)存储器可以使用 EMIF 进行访问。请参见第 24页上的外部存储器接口。

表 5-5. XDATA 数据地址映射

| 地址范围                  | 用途                       |

|-----------------------|--------------------------|

| 0×00 0000 – 0×00 1FFF | SRAM                     |

| 0×00 4000 – 0×00 42FF | 时钟、PLL 和振荡器              |

| 0×00 4300 – 0×00 43FF | 电源管理                     |

| 0×00 4400 – 0×00 44FF | 中断控制器                    |

| 0×00 4500 – 0×00 45FF | 端口中断控制                   |

| 0×00 4700 – 0×00 47FF | 闪存编程接口                   |

| 0×00 4800 - 0×00 48FF | 缓存控制器                    |

| 0×00 4900 – 0×00 49FF | I <sup>2</sup> C 控制器     |

| 0×00 4E00 – 0×00 4EFF | 抽取滤波器                    |

| 0×00 4F00 – 0×00 4FFF | 固定定时器 / 计数器 /PWM         |

| 0×00 5000 – 0×00 51FF | I/O 端口控制                 |

| 0×00 5400 – 0×00 54FF | 外部存储器接口 (EMIF) 控制<br>寄存器 |

| 0×00 5800 – 0×00 5FFF | 模拟子系统接口                  |

| 0×00 6000 – 0×00 60FF | USB 控制器                  |

| 0×00 6400 – 0×00 6FFF | UDB 工作寄存器                |

| 0×00 7000 – 0×00 7FFF | PHUB 配置                  |

| 0×00 8000 – 0×00 8FFF | EEPROM                   |

| 0×00 A000 – 0×00 A400 | CAN                      |

| 0×00 C000 - 0×00 C800 | 数字滤波器模块                  |

| 0×01 0000 – 0×01 FFFF | 数字互连配置                   |

| 0×05 0220 – 0×05 02F0 | 调试控制器                    |

| 0×08 0000 – 0×08 1FFF | 闪存 ECC 字节                |

| 0×80 0000 – 0×FF FFFF | 外部存储器接口                  |

# 6. 系统集成

# 6.1 时钟系统

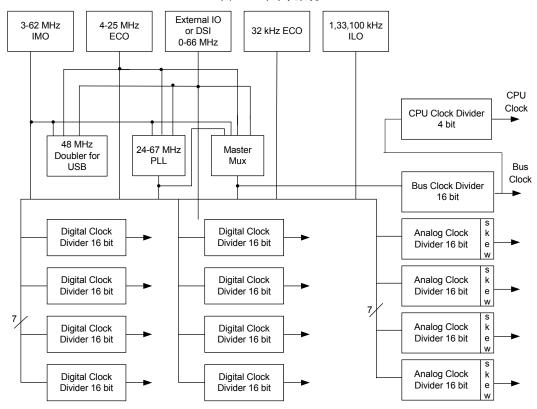

时钟系统负责整个 PSoC 系统内的时钟生成、分频和分配工作。对于大多数系统,均不需要额外的外部晶振。结合使用 IMO 和 PLL,可以生成高达 66 MHz 的时钟,且在有效工作电压和温度下,该时钟的精度为±1%。通过使用额外的内部和外部时钟源,可以根据设计需要优化准确度、功耗和成本。所有系统时钟源都可以用于在 16 位时钟分频器和 UDB 中为用户所需的任何部件(例如 UART 波特率生成器)生成其他时钟频率。

时钟生成和分配是根据整个系统的要求,通过 PSoC Creator IDE 图形界面自动配置。这是基于完整的系统要求而定的,能够极大地加快设计进程。利用 PSoC Creator,您只需进行极少的输入,即可构建时钟系统。您可以指定所需的时钟频率和精度,软件将定位或构建符合所需规范的时钟。这得益于 PSoC 固有的可编程性。

时钟系统的关键特性包括:

- ■七个通用时钟源

- □ 3 至 62 MHz IMO, 在 3 MHz 下精度为 ±1%

- □4至25 MHz外部晶振 (MHzECO)

- □ 时钟倍频器能够为 USB 模块提供双倍时钟频率输出,请参见第 29 页上的 USB 时钟域。

- □来自外部 I/O 引脚或其他逻辑的 DSI 信号

- □源自IMO、MHzECO或DSI的24至67MHz小数分频锁相环

- □用于WDT和睡眠定时器的1kHz、33kHz、100kHzILO

- □用于实时时钟的 32.768 kHz 外部晶体或晶振 (kHzECO)

- IMO 具有 USB 模式,在该模式下,无需对 USB 使用任何外部晶振,即可自动锁定到 USB 总线时钟(仅限于配备 USB 的器件)

- ■所有时钟分频器中的时钟源都是独立的

- ■用于数字系统的八个 16 位时钟分频器

- ■用于模拟系统的四个 16 位时钟分频器

- ■用于总线时钟的专用 16 位分频器

- ■用于总线时钟的专用4位分频器

- 在 PSoC Creator 中自动进行时钟配置

# 图 6-1. 时钟子系统

# 表 6-1. 振荡器汇总

| 时钟源    | 最低频率   | 最低频率容限             | 最高频率    | 最高频率容限      | 启动时间                    |

|--------|--------|--------------------|---------|-------------|-------------------------|

| IMO    | 3 MHz  | 有效工作电压和温度下,精度为 ±1% | 62 MHz  | ±7%         | 最大值 13 µs               |

| MHzECO | 4 MHz  | 取决于晶振              | 25 MHz  | 取决于晶振       | 典型值 5 ms,最大值<br>取决于晶振   |

| DSI    | 0 MHz  | 取决于输入              | 66 MHz  | 取决于输入       | 取决于输入                   |

| PLL    | 24 MHz | 取决于输入              | 67 MHz  | 取决于输入       | 最大值 250 µs              |

| 倍频器    | 48 MHz | 取决于输入              | 48 MHz  | 取决于输入       | 最大值 1 µs                |

| ILO    | 1 kHz  | _50%、 +100%        | 100 kHz | _55%、 +100% | 在最低功耗模式下的<br>最大值为 15 ms |

| kHzECO | 32 kHz | 取决于晶振              | 32 kHz  | 取决于晶振       | 典型值 500 ms,最<br>大值取决于晶振 |

### 6.1.1 内部振荡器

图 6-1 显示了两个内部振荡器。它们可以被直接路由或分频。这些直接路由可能没有50%的占空比周期,而分频的时钟具有50%的占空比周期。

### 6.1.1.1 内部主振荡器

由于 IMO 的精度可以达到 ±1%,因此,在大多数设计中,只需要这一个时钟源即可。IMO 工作时不需要任何外部组件,并能够输出稳定的时钟。各频率范围的出厂预设值存储在器件中。使用出厂预设值时,容差介于 ±1%(在 3 MHz 下)到 ±7%(在 62 MHz 下)之间。 IMO 与 PLL 结合使用时,可以生成达到器件最高频率的其他时钟(请参见锁相环)。

IMO 可提供 3、6、12、24、48 和 62 MHz 的时钟输出。

### 6.1.1.2 时钟倍频器

时钟倍频器能够输出频率为输入时钟频率两倍的时钟。倍频器能够处理 24 MHz 的输入频率,且使用 USB 时可达 48 MHz。 它可以配置为使用来自 IMO、MHzECO 或 DSI (外部引脚)的时钟。

### 6.1.1.3 锁相环

借助 PLL,可将低频率、高准确度时钟倍增至频率更高的时钟。 这是高时钟频率和准确度以及高功耗和较长启动时间之间的博 弈。

PLL 模块提供了基于各种输入源生成时钟频率的机制。PLL 输出的时钟频率介于 24 到 67 MHz 之间。其输入和反馈分频器提供了 4032 个离散率,能够生成几乎任何所需的时钟频率。 PLL 输出的精度取决于 PLL 输入源的精度。最常见的 PLL 用法是在 3 MHz 下倍增 IMO 时钟,因为在该频率下生成的其他时钟精度最高,并能够达到器件的最大频率。

PLL 能够在 250 μs 内实现相位锁定(通过位设置进行验证)。它可以配置为使用来自 IMO、 MHzECO 或 DSI (外部引脚)的时钟。在锁定完成并发出锁定位信号之前,可以一直使用 PLL 时钟源。锁定信号可通过 DSI 连接,以便生成中断。在进入低功耗模式之前请禁用 PLL。

### 6.1.1.4 内部低速振荡器

ILO 能够提供可实现低功耗的时钟频率,包括为看门狗定时器和睡眠定时器提供时钟频率。ILO 能够生成多达三个不同的时钟,即: 1 kHz、33 kHz 和 100 kHz。

**1 kHz** 时钟(CLK1K)通常用于后台 "心跳式" 定时器。该时钟旨在进行低功耗监控操作,例如,采用中央时轮(CTW)的看门狗定时器和长睡眠间隔。

中央时轮是一个以 1 kHz 频率自由运行的 13 位计数器,其时钟由 ILO 提供。除非处于休眠模式或在片上调试模式期间 CPU 处于停止状态,否则中央时轮始终处于使能状态。它可用于生成定期中断以便提供时序,也可用于从低功耗模式唤醒系统。通过固件可以复位中央时轮。需要精确时序的系统应采用实时时钟 RTC 功能,而非中央时轮。

**100 kHz** 时钟(CLK100K)可作为低功耗主设备时钟。它也可以生成使用快速时轮的时间间隔。

快速时轮是一个 5 位计数器,它的源为 100 kHz 时钟。它的设置是可编程的,当计数结束时将自动复位。每当计数结束时可以生成一个可选中断。从而能够以高于使用中央时轮时所能达到的频率灵活地定期生成 CPU 中断。

33 kHz 时钟 (CLK33K) 是对 CLK100K 进行三分频后获得的。 该输出可用作低准确度版 32.768 kHz ECO 时钟 (无需使用晶振)。

# 6.1.2 外部振荡器

图 6-1 还显示了两个外部振荡器。可以将它们直接传输或分频。直接传输时的占空比不会超过 50%。分频时钟则具有 50% 的占空比。

# 6.1.2.1 MHz 外部晶振

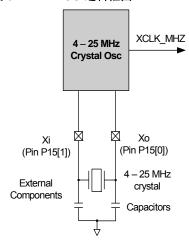

通过采用外部晶体,MHzECO 能够提供高频率、高准确度时钟(请参见图 6-2)。它支持大量的晶体类型,频率范围介于 4 到 25 MHz 之间。与 PLL 结合使用时,它可以生成达到器件最高频率的其他时钟(请参见锁相环)。连接到外部晶振和电容的 GPIO 引脚是固定的。MHzECO 的准确度取决于所选择的晶振。

# 图 6-2. MHzECO 逻辑框图

# 6.1.2.2 32.768 kHz ECO

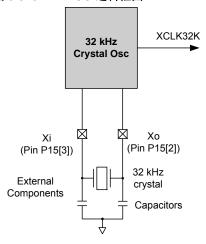

通过使用外部 32.768 kHz 时钟晶振, 32.768 kHz 外部晶振 (32kHzECO) 能够以非常低的功耗提供精确时序 (请参见图 6-3)。32kHzECO 还直接连接到睡眠定时器,并为实时时钟提供时钟源。RTC 通过使用 1 秒中断在固件中实现 RTC 功能。

该振荡器能够采用两种不同的功耗模式,以便用户在功耗和抗周 围电路噪声之间进行权衡。连接到外部晶振和电容的 GPIO 引脚 是固定的。

# 图 6-3. 32kHzECO 逻辑框图

建议外部 32.768 kHz 时钟晶振的负载电容(CL)为 6 pF 或 12.5 pF。查看晶振制造商的数据手册。两个外部电容器 CL1和 CL2 通常具有相同值,其总计电容 CL1CL2/(CL1+CL2)应等于晶振 CL 的值,其中包含引脚和走线电容。更多有关信息,请参见应用笔记 AN54439: PSoC 3 和 PSoC 5 外部振荡器。另请参见第78页上的 GPIO 中的引脚电容规范。

# 6.1.2.3 数字系统互连

对于来自与 I/O 相连的外部时钟振荡器的时钟, DSI 能够为其提供路由。这些振荡器也可以在数字系统和 UDB 内生成。

虽然主要 DSI 时钟输入提供对所有时钟资源的访问,但有多达八个其他 DSI 时钟(在内部或外部生成)可直接连接到八个数字时钟分频器。不过,这需要有多个高准确度时钟源才能实现。

# 6.1.3 时钟分配

所有七个时钟源都是中央时钟分配系统的输入。分配系统旨在创建多个高准确度时钟。这些时钟是针对设计需求定制的,能够避免在连接到外设的低分辨率预分频器上经常遇到的一些问题。时钟分配系统能够生成多种类型的时钟树。

- ■主设备时钟用于选择和提供系统中的最快时钟,以满足一般的时钟要求,并使 PSoC 器件实现时钟同步。

- 总线时钟 16 位分频器采用系统时钟来生成总线时钟,以用于数据传输。总线时钟是 CPU 时钟分频器的源时钟。

- ■八个完全可编程的 16 位时钟分频器能够按照设计需求,为数字系统生成通用的数字系统时钟。数字系统时钟可以针对任何用途生成由七个时钟源中的任何一个时钟源派生而来的定制时钟,例如用于波特率生成器、精确的 PWM 周期、定时器时钟等。如果需要八个以上的数字时钟分频器,通用数字模块(UDB)和固定功能定时器/计数器/PWM 也可以生成时钟。

- ■四个 16 位时钟分频器负责为需要时钟的模拟系统组件 (如 ADC 和混频器)生成时钟。模拟时钟分频器包括时滞 (Skew)控制功能,用于确保关键模拟事件不会与数字切换事件同时发生。其目的是为了减少模拟系统噪声。

每个时钟分频器均包含一个 8 输入复用器、一个 16 位时钟分频器(二分频或更高分频,能够生成占空比约为 50% 的时钟)、主设备时钟重新同步逻辑,以及抗尖峰脉冲逻辑。每个数字时钟树的输出均可连接至数字系统互连,然后再作为输入返回到时钟系统,从而实现高达 32 位的时钟链。

# 6.1.4 USB 时钟域

USB 时钟域的独特性在于,它在工作时与主时钟网络存在很大程度的异步。USB 逻辑包含连接到芯片的同步总线接口,但会采用异步时钟来运行,以便处理 USB 数据。USB 逻辑需要 48 MHz的频率。该频率可以使用不同的时钟源生成,其中包括由内部振荡器、DSI 信号或晶振生成的 48 MHz(或 24 MHz 的双倍值)的 DSI 时钟。

# 6.2 供电系统

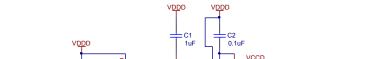

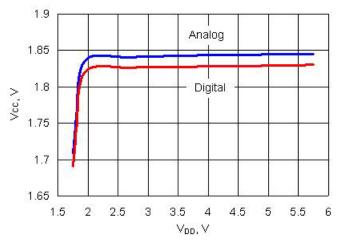

供电系统包含单独的模拟、数字和 I/O 供电引脚,标记分别为 VDDA、 VDDD 和 VDDIO×。此外,还包含两个内部 1.8 V 电压调 节器,以便为内部内核逻辑提供数字(VCCD)和模拟(VCCA)供电。电压调节器的输出引脚(VCCD 和 VCCA)和

VDDIO 引脚必须连接电容,如图 6-4 所示。两个 VCCD 引脚必须连接在一起,引脚之间的线路越短越好,并连接到一个 1 μF ±10% ×5R 电容器上。供电系统还包含睡眠电压调节器、 I<sup>2</sup>C 电压调节器和休眠电压调节器。

### 图 6-4. PSoC 供电系统 1 μF VDDIO2 VDDI00 $\leftarrow$ 0.1 μF 0.1μF **VSSD** /DDD I/O Supply I/O Supply VDDI00 0.1 μF I2C Regulator Sleep Regulator Digital VDDA Domain VDDA VCCĄ Analog Regulator Digital Regulators 0.1μF VSSB $\forall$ VSS Analog Domain Hibernate Regulator VDDIO1 I/O Supply I/O Supply 0.1μF -||-0.1 μF VDDIO1 VDDD VDDI03

# 注意:

- ■两个 Vccd 引脚必须连接在一起,并且之间的线路越短越好。建议在器件下方连接线路,如第 12 页上的图 2-8。

- 查看数据手册要求的旁路电容值是一个好的习惯,特别是工作电压和直流偏置规范。对于一些电容器,如果直流偏置电压 (图 6-4 中的 VDDX 或 VCCX)占额定工作电压的比例比较大,那么实际电容则明显降低。

- 您可以在内部调节模式下供电给器件,其中,VDDx 引脚的电压为 5.5 V,并且内部调节器提供了内核电压。**在该模式下,不要供电给 VCCx 引脚,并且不要将 VDDx 引脚连接至 VCCx 引脚。**

- 您也可以为 VCCD 和 VCCA 直接提供电压,从而能够在外部调节模式下供电给器件。在该配置中,VDDD 引脚短接 VCCD 引脚,则 VDDA 引脚短接 VCCA 引脚。该配置中的允许供电电压范围为 1.71 V 至 1.89 V。在该配置中上电后,默认使能内部调节器,因此需要禁用该调节器以便减少功耗。

# 6.2.1 功耗模式

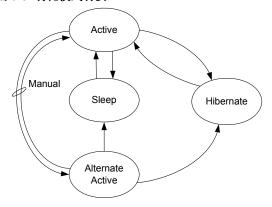

PSoC 3 器件具有四种不同的功耗模式,如表 6-2 和表 6-3 所示。借助这些功耗模式,设计能够轻松提供所需的功能和处理能力,同时最大限度地减小低功耗便携器件的功耗并提高其电池寿命。旨在降低功耗的 PSoC 3 功耗模式包括:

- ■活动模式

- ■备用活动模式

- ■睡眠模式

- ■休眠模式

# 表 6-2. 功耗模式

活动模式是主要处理模式。其功能是可配置的。通过使用单独的功耗配置样本寄存器,可以使能或禁用每个功耗可控子系统。在备用活动模式模式下,会使能较少的子系统,从而能够降低功耗。在睡眠模式下,无论采用什么样的样本设置,大多数资源都将处于禁用状态。睡眠模式已经过优化,能够提供定时睡眠间隔和实时时钟(RTC)功能。功耗最低的是休眠模式,该模式会保留寄存器和 SRAM 状态,但会关闭时钟,并且只能通过 I/O 引脚唤醒。图 6-5 显示了在各种功耗模式之间允许进行的切换。不应进入睡眠和休眠模式,直到所有 VDDIO 达到有效电压时为止。

| 功耗模式       | 说明                                                                          | 进入条件                | 唤醒源                                                 | 活动时钟    | 电压调节器                                                           |  |  |  |

|------------|-----------------------------------------------------------------------------|---------------------|-----------------------------------------------------|---------|-----------------------------------------------------------------|--|--|--|

| 活动模式       | 主要的工作模式,所有外设均可用(可编程)                                                        | 唤醒、复位、通过寄<br>存器手动进入 | 任意中断                                                | 任意(可编程) | 所有电压调节器均可用。如果采用了外部电压调节器,则可以禁<br>用数字和模拟电压调节器。                    |  |  |  |

| 备用活动<br>模式 | 与活动模式相似,配置为此模式通常是为了让更少的外设处于活动状态,以便降低功耗。可以配置为:关闭CPU,并使用 UDB 进行处理             | 入                   | 任意中断                                                |         | 所有电压调节器均可用。如果采<br>用外部电压调节器,则可以禁用<br>内部数字和模拟电压调节器。               |  |  |  |

| 睡眠模式       | 会自动禁用所有子系统                                                                  | 通过寄存器手动进入           | 比 较 器、<br>PICU、I <sup>2</sup> C、<br>RTC、CTW、<br>LVD |         | 数字和模拟统电压调节器均处于 BUZZ 状态 (周期性激活)。<br>如果采用外部电压调节器,则可以禁用数字和模拟电压调节器。 |  |  |  |

| 休眠模式       | 自动禁用所有子系统。<br>最低功耗模式,所有外设和内部电压<br>调节器均处于禁用状态,仅使能休眠<br>电压调节器。<br>保持配置和存储器的内容 | 通过寄存器手动进入           | PICU                                                | _       | 只有休眠电压调节器被激活。                                                   |  |  |  |

# 表 6-3. 功耗模式唤醒时间和功耗

| 睡眠模式       | 唤醒<br>时间 | 电流<br>(典型值)            | 代码执行 | 数字资源             | 模拟资源 | 可用<br>时钟源  | 唤醒源                                           | 复位源              |

|------------|----------|------------------------|------|------------------|------|------------|-----------------------------------------------|------------------|

| 活动模式       | _        | 1.2 mA <sup>[16]</sup> | 是    | 全部               | 全部   | 全部         | -                                             | 全部               |

| 备用活动<br>模式 | -        | 1                      | 用户定义 | 全部               | 全部   | 全部         | -                                             | 全部               |

| 睡眠模式       | <15 µs   | 1 μΑ                   | 否    | I <sup>2</sup> C | 比较器  | ILO/kHzECO | 比较器、PICU、<br>I <sup>2</sup> C、RTC、<br>CTW、LVD | XRES、<br>LVD、WDR |

| 休眠模式       | <100 µs  | 200 nA                 | 否    | 无                | 无    | 无          | PICU                                          | XRES             |

### 注释

16. 总线时钟关闭。在 6 MHz 频率下从缓存中执行。请参见第 70 页上的表 11-2。

# 图 6-5. 功耗模式切换

# 6.2.1.1 活动模式

活动模式是器件的主要工作模式。当处于活动模式时,活动配置样本位将控制使能或禁用哪些可用资源。当有资源处于禁用状态时,系统会关断数字时钟,禁用模拟偏置电流,并相应地减少漏电流。通过在活动配置样本中设置和清除相应的位,用户固件可以动态控制子系统的功耗。CPU可以自我禁用,在这种情况下,发生下一个唤醒事件时会自动重新使能 CPU。

在发生唤醒事件时,全局模式始终会返回到活动模式,并且会自动使能 CPU,而不管它采用什么样的样本设置。活动模式是引导时的默认全局功耗模式。

### 6.2.1.2 备用活动模式

备用活动模式与活动模式非常类似。在备用活动模式下,会使能较少的子系统,以便降低功耗。一种可能的配置是:关闭 CPU 和闪存,并使外设全速运行。

# 6.2.1.3 睡眠模式

如果可以接受 15 μs 的恢复时间,则可以采用睡眠模式来降低功耗。唤醒时间用于确保电压调节器的输出足够稳定,以便直接进入活动模式。

# 6.2.1.4 休眠模式

在休眠模式下,几乎所有内部功能都将处于禁用状态。内部电压会降至使关键系统保持活动状态所需的最低水平。在休眠模式下,会保留配置状态和 SRAM 存储器的内容。配置为数字输出的GPIO 将保留其先前的值,并且外部 GPIO 引脚中断设置也将保留。器件处于休眠模式时,只能通过外部 I/O 中断唤醒。从休眠模式恢复的时间不会超过 100 µs。

为了实现极低的电流,休眠调节器的性能有所限制。输入引脚上的所有信号频率被限制;在休眠模式下切换 GPIO 的频率不会高

于 10 kHz。在低功耗模式下,如果需要以高速度进行切换,需要选择睡眠模式。

# 6.2.1.5 唤醒事件

唤醒事件是可以配置的,并且可以来自中断或器件复位。唤醒事件会将系统恢复到活动模式。固件使能的中断源包括内部生成的中断、功耗监控器、中央时轮和 I/O 中断。内部中断源可以来自各种外设,如模拟电压比较器和 UDB。中央时轮会提供定期中断,以便唤醒系统、轮询外设或执行实时功能。复位事件源包括外部复位 I/O 引脚(XRES)、WDT 和精密复位(PRES)。

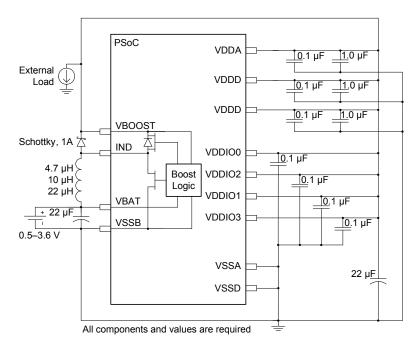

### 6.2.2 升压转换器

采用 1.71 V 以下供电电压 (例如,太阳能供电或单个电池供电)的应用可以使用片上升压转换器。升压转换器还可以用于所需工作电压高于供电电压的任何系统。例如,在 3.3 V 系统中驱动 5.0 V LCD 显示屏。升压器可以接受的最低输入电压为 0.5 V。通过一个低成本电感,它可以生成一个可选输出电压,以便提供足够的电流来运行 PSoC 及其他板上组件。

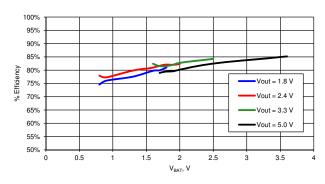

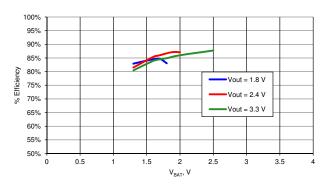

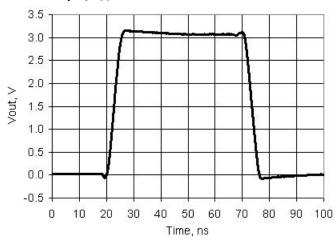

升压转换器可以接受介于 0.5 V 到 3.6 V 之间的输入电压 (VBAT),可使用低至 0.5 V 的 VBAT 进行启动,并能够提供介于 1.8 到 5.0 V 之间、可由用户配置的输出电压 (VOUT),其步长为 100 mV。 VBAT 通常小于 VOUT;如果 VBAT 大于或等于 VOUT,那么 VOUT 会略小于 VBAT (由于升压器中的电阻损耗)。该模块可以提供高达 75 mA (IBOOST)的电流,具体取决于配置。

有四个与升压转换器相关联的引脚,即: VBAT、VSSB、VBOOST以及IND。提升后的输出电压通过VBOOST引脚输出,并且如果使用该电压供电给 PSoC 器件,那么必须直接连接到芯片的供电输入: VDDA、VDDD 和 VDDIO。

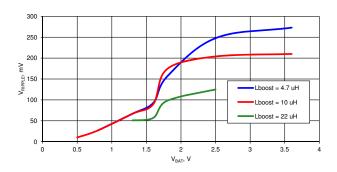

除了非升压设计中所需的组件,该升压转换器还需要添加四个组,如第33页上的图6-6所示。需要将一个22 μF的电容(C<sub>BAT</sub>)靠近 VBAT 引脚,对电池电压起缓冲和滤波稳定作用。电池输出与 VBAT 引脚之间不要添加其它器件,例如反向极性保护二极管。因为二极管正向电压下降将使 V<sub>BAT</sub> 电压下降。在 VBAT 和IND 引脚间需要 4.7 μH、10 μH或 22 μH的电感。根据输入电压、输出电压、温度和电流,可以优化电感值以提高升压转换器的效率。按照本节中的设计指南和电气规范来决定电感尺寸。电感必须被放置在离 VBAT 和 IND 引脚 1 cm 范围内,其饱和电流的最小值为 750 mA。在 IND 和 VBOOST 引脚间 1 cm 范围内,放置一个肖特基二极管。该肖特基二极管的正向电流最小额定值为 1.0 A,反向电压最小值为 20 V。将大小为 22 μF 的大容量电容(CBOOST)连接到靠近 VBOOST 的位置,以便提供稳定的输出电压。需要计算连接至 VBOOST 引脚的电容总和并确保该值不超过最大 CBOOST 规范。所有电容的最小额定值必须为 10 V 以最大限度降低电压降额带来的电容损失。

图 6-6. 升压转换器的应用 (为 PSoC 器件供电)

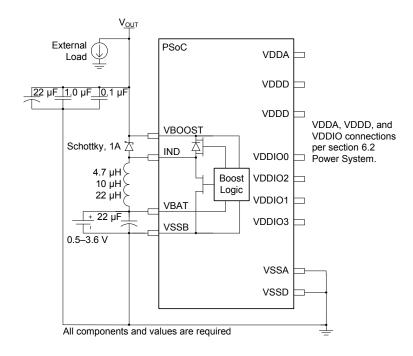

升压调节器也可以用于为其它的外部器件供电,下图是一个将 1.8 V 的电源升压到 4.0,用于驱动一个白色 LED 便是这种情况的一个示例 。如果升压转换器不为 PSoC 器件的  $V_{DDA}$ 、  $V_{DDD}$  和  $V_{DDIO}$  引脚供电,那么它必须符合为 PSoC 器件供电的同一个设计规则,但对于输出端的电容有不同的要求。Vout 电源需要安装 22  $\mu$ F、1.0  $\mu$ F 和 0.1  $\mu$ F 等电容器,这些电容器必须被放置在离 VBOOST 引脚 1 厘米的范围内,以确保电压调节器的稳定性。

图 6-7. 升压转换器的应用 (未给 PSoC 器件供电)

使用升压器模块中的振荡器将切换频率设为 400 kHz。VBOOST被限定为 4 × VBAT。

升压转换器可以在两种不同模式下工作:即活动模式和待机模式。活动模式是正常工作模式,在此模式下,升压调节器会主动生成稳压输出电压。在待机模式下,大多数升压功能都将处于禁用状态,以便降低升压电路的功耗。待机模式下,升压器仅提供最低的输出功耗,通常 < 5 μA。

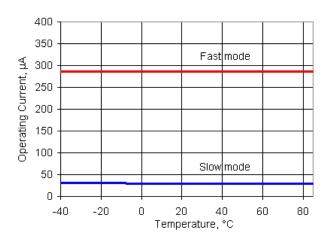

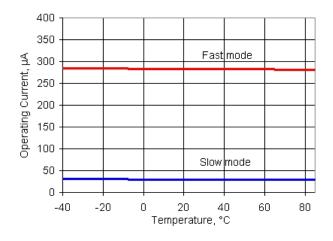

升压转换器在活动模式下消耗的电流通常为250 μA, 在待机模式下则为25 μA。升压工作模式必须与芯片功耗模式结合使用,以便最大限度地降低芯片总功耗。表 6-4 列出了在不同芯片功耗模式下可用的升压功耗模式。

# 表 6-4. 芯片功耗模式与升压功耗模式兼容表

| 芯片功耗模式               | 升压功耗模式                                                           |

|----------------------|------------------------------------------------------------------|

| 芯片 — 活动模式或备<br>用活动模式 | 升压转换器必须采用活动模式。                                                   |

| 芯片 — 睡眠模式            | 升压转换器既可以采用活动模式,也可以采用待机模式。在升压待机模式中,芯片必须定期唤醒,以刷新升压活动模式。            |

| 芯片 — 休眠模式            | 升压转换器只能在活动模式下运行。不过,由于在升压活动模式下的电流消耗<br>非常高,因此不建议在芯片休眠模式下<br>使用升压。 |

# 6.2.2.1 升压固件的要求

要想确保启动时升压浪涌电流符合规范,在 PSoC Creator IDE 中不要选中 Enable Fast IMO During Startup (启动期间使能快速 IMO) 值。 Enable Fast IMO During Startup 选项会显示在 PSoC Creator 的设计 范围资源(cydwr)文件 System(系统)选项卡中。 如果未选中该选项会配置器件启动时的运行速度为 12 MHz 而不是默认的 48 MHz。时钟速度越慢,芯片启动时升压电路的电流消耗越少。

# 6.2.2.2 升压设计过程

升压转换器的外部器件选型需要遵守特定的规范。 $C_{BAT}$  电容器、电感、肖特基二极管和  $C_{BOOST}$  电容器的选择都需要遵守规范(第 76 页上的表 11-7)中指定的值。 $L_{BOOST}$  是唯一的变量组件,选择合适的升压电感不仅可以改善升压转换器的运行状态,还可以提高转换效率。此外, $V_{OUT}$ 、 $V_{BAT}$ 、 $I_{OUT}$  和  $I_{A}$  之间还存在特定的限制关系。

必须按照以下各步骤进行操作,以确定升压转换器的操作参数和 L<sub>BOOST</sub> 值。

- 1. 选择应用所需的 V<sub>BAT</sub>、 V<sub>OUT</sub>、 T<sub>A</sub> 和 I<sub>OUT</sub> 等工作条件。

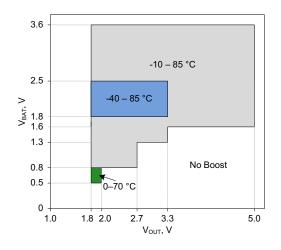

- 2. 根据**与 V<sub>BAT</sub> 和 V<sub>OUT</sub> 相比的 T<sub>A</sub> 范围**图表 (第 76 页上的图 11-8)确定 V<sub>BAT</sub> 和 V<sub>OUT</sub> 规范是否符合升压转换器的工作范围。如果不符合工作范围,则更改工作条件或使用一个外部升压调节器。

- 3. 根据与 V<sub>BAT</sub> 和 V<sub>OUT</sub> 相比的 T<sub>A</sub> 范围图表 (第 76 页上的图 11-8)确定所需环境温度 (T<sub>A</sub>)范围是否符合环境温度工作范围。如果不符合温度范围,则更改工作条件并返回步骤 2,或使用一个外部升压调节器。

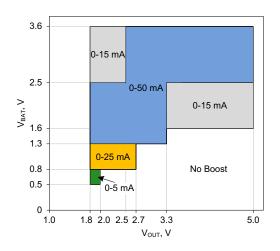

- 4. 根据与 **V<sub>BAT</sub> 和 V<sub>OUT</sub> 相比的 I<sub>OUT</sub> 范围**图表 (第 76 页上的图 11-9)确定所需输出电流(I<sub>OUT</sub>)范围是否满足输出电流工作范围。如果不符合输出电流范围,则更改工作条件并返回步骤 **2**,或使用一个外部升压调节器。

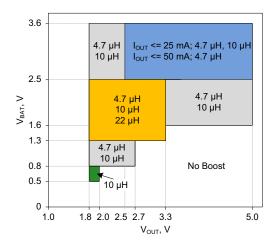

- 5. 根据**与 V<sub>BAT</sub> 和 V<sub>OUT</sub> 相比的 L<sub>BOOST</sub> 值**图表 (第 76 页上的 图 11-10) 查找可用电感值。

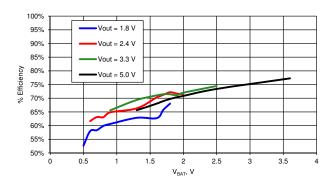

- 6. 根据可用电感值、电感尺寸、电感成本、升压效率和 V<sub>RIPPLE</sub> 选择系统的最佳电感值。升压效率和 V<sub>RIPPLE</sub> 典型值将分别显示在**效率与 V<sub>BAT</sub>** 和 V<sub>RIPPLE</sub> 与 V<sub>BAT</sub> 图表 (第 79 页上的图 11-15 和第 81 页上的图 11-18)中。通常,如果高效率和低 V<sub>RIPPLE</sub> 是两个最重要的因素,因此应该使用允许的最大电感值。如果电感成本低、尺寸小是最重要因素,则应该使用其中一个允许的最小电感值。如果对于应用,电感的允许效率、 V<sub>RIPPLE</sub>、电感成本或尺寸都不可接受,那么需要使用一个外部升压调节器。

# 6.3 复位

CY8C36 有多个内部和外部复位源可用。其中包括:

- ■电源监控 在加电、活动模式以及睡眠模式(间歇性唤醒)期间,在多种不同模式下监控模拟和数字供电电压 VDDA、 VDDD、VCCA 和 VCCD。如有任何电压超出预定范围,则会 生成复位。可以对监控器进行编程,以便在到达复位阈值之 前,在特定条件下生成处理器中断。

- 外部 通过拉低复位引脚(XRES),可以从外部源复位器件。XRES 引脚包含一个上拉到 VDDIO1 的内部电阻。VDDD、VDDA 和 VDDIO1 必须都通电,器件才能退出复位状态。

- 看门狗定时器 看门狗定时器负责监控处理器执行指令的情况。如果看门狗定时器在特定时间段内未通过固件复位,则会生成一个复位。

- 软件 器件可以在程序控制下复位。

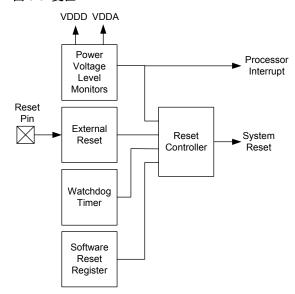

# 图 6-8. 复位

器件复位一词指处理器以及模拟和数字外设与寄存器都复位。

复位状态寄存器显示了某些复位或供电电压的监控中断。程序可能会检查该寄存器,以检测并报告异常情况。加电复位后,会清空该寄存器。有关详细信息,请参见《技术参考手册》。

# 6.3.1 复位源

# 6.3.1.1 供电电压电平监控器

# ■ IPOR — 初始 POR

在初次上电复位时, IPOR 会监控电源电压 V<sub>DDD</sub>、 VDDA、 VCCD 以及 VCCA。触发电平并不精确。该电平被设为约 1 V, 低于指定的最低工作电压,但足以使内部电路复位并保持复位 状态。 监控器能够生成宽度至少为 150 ns 的复位脉冲。 如果有 一个或多个电压缓慢上升,生成的脉冲可能会更宽。

如果 IPOR 触发任一  $V_{DDX}$  后,电压又降落并低于触发点,那么必须以非单调格式至少在 10  $\mu$ s 时间内保持这个电压水平。 IPOR 触发点的迟滞通常为 100 mV。

启动后, IPOR 电路被禁用,并且电压监控工作将移交给精密 低电压复位 (PRES) 电路。

# ■ PRES — 精密低电压复位

此电路负责在加电后监控模拟系统和数字系统内部电压调节器 的输出。电压调节器的输出是相对于精确参考电压的电压。对 PRES 激发的响应与对 IPOR 复位的响应相同。

禁用 PRES 时,至少 10 μs 后才可重新使能它。

在正常工作模式下,程序无法禁用数字 PRES 电路。可以禁用 模拟系统电压调节器,但这会同时禁用 PRES 的模拟部分。在 睡眠和休眠模式下, PRES 电路自动被禁用, 但是也有例外, 即: 在睡眠模式下, 会定期激活电压调节器 (使其处于繁忙状 态),以便提供监控服务,并缩短唤醒时间。与此同时,PRES 电路也将处于繁忙状态,以便定期进行电压监控。

■ ALVI、DLVI、AHVI — 模拟 / 数字低电压中断,模拟高电压中断 中断电路可用于检测 VDDA 和 VDDD 超出电压范围的情况。对 于 AHVI, VDDA 是相对于某个固定触发电平的电压。对于 ALVI 和 DLVI, VDDA 和 VDDD 是相对于可编程触发电平的电压, 如表 6-5 中所列。ALVI 和 DLVI 也可以被配置为生成器件复位, 而不是生成中断。

表 6-5. 模拟/数字低电压中断,模拟高电压中断

| 中断   | 供电源  | 正常电压范围         | 可用的触发设置                        |

|------|------|----------------|--------------------------------|

| DLVI | VDDD | 1.71 V – 5.5 V | 1.70 V-5.45 V,最小增量<br>为 250 mV |

| ALVI | VDDA | 1.71 V – 5.5 V | 1.70 V-5.45 V,最小增量<br>为 250 mV |

| AHVI | VDDA | 1.71 V – 5.5 V | 5.75 V                         |

在 IPOR 之前,监控器将一直处于禁用状态。在睡眠模式下, 会定期激活这些电路 (使其处于繁忙状态)。在繁忙状态期间 如有中断发生,系统会首先进入唤醒过程。然后,系统会识别 中断, 并可能会处理中断。

Buzz (繁忙) 频率是可调整的,并且需要设置该频率低于任-电压超出允许范围的最短时间。有关如何调整繁忙频率的信 息,请参见《技术参考手册》。

# 6.3.1.2 其他复位源

■ XRES — 外部复位

PSoC 3 具有一个被配置为外部复位的 GPIO 引脚或一个专用 XRES 引脚。无论是专用 XRES 引脚还是 GPIO 引脚,配置后, 都会使部件处于复位状态,同时保持低电平有效。对 XRES 的 响应与对 IPOR 复位的响应相同。

禁用 XRES 时,至少 10 μs 后才可重新使能它。

17. Opamp 的固有输出引脚不建议用作 CapSense 功能。

外部复位是低电平有效复位。它包含一个内部上拉电阻。在睡 眠模式和休眠模式下, XRES 将处于活动状态。

# ■ SRES — 软件复位

通过在软件复位寄存器中设置一个位, 可以在程序控制下发出 复位指令。这可以通过程序直接进行,也可以通过 DMA 访问 间接进行。对 SRES 的响应与对 IPOR 复位的响应相同。 此外还有另外一个寄存器位,用于禁用此功能。

# ■ WRES — 看门狗定时器复位

看门狗复位会检测软件程序不再正常执行的情况。为了向看门 狗定时器表明它正在正常工作,程序必须定期复位该定时器。 如果在经过用户指定的时间后未复位该定时器,则会生成复

注意: IPOR 会禁用看门狗功能。程序必须通过设置寄存器位, 在代码中的某个适当点使能看门狗功能。设置寄存器位后,将 无法再将其清除,除非发生 IPOR 加电复位事件。

# 6.4 I/O 系统与布线

PSoC I/O 具有高度的灵活性。每个 GPIO 都具有模拟和数字 I/O 功能。所有 I/O 都具有多种可在 POR 时设置的驱动模式。PSoC 还通过 VDDIO 引脚提供多达四个 I/O 电压域。

每个器件上都有两种 I/O 引脚; 带 USB 的器件则有三种 I/O 引 脚。通用 I/O (GPIO) 和特殊 I/O (SIO) 提供类似的数字功能, 主要区别在于模拟能力和驱动强度。带 USB 的器件还提供两个 USBIO 引脚,可支持特定的 USB 功能,以及有限的 GPIO 功能。

所有 I/O 引脚均可作为 CPU 与数字外设的数字输入和输出使用。 此外,所有 I/O 引脚均可生成中断。PSoC I/O 具有灵活的高级功 能,再加上任意信号均可连接至任意引脚,从而大大简化了电路 设计和电路板布局。所有 GPIO 引脚均可用于模拟输入、CapSense $^{[17]}$ 以及 LCD 段驱动,而 SIO 引脚用于超出 VDDA 的 电压和可编程输出电压。

- GPIO 和 SIO 均支持的特性:

- □用户可编程端口复位状态

- □ 为多达四组 I/O 提供单独的 I/O 供电和电压

- □ 数字外设使用 DSI 连接引脚

- □用于 CPU 和 DMA 的输入和 / 或输出

- □八种驱动模式

- □每个引脚都可以是一个被配置为上升沿和 / 或下降沿的中断 源。如有必要,可通过 DSI 支持电平敏感型中断

- □每个端口都有专用的端口中断向量

- □斜率受控数字输出驱动模式

- □基于端口或引脚访问端口控制和配置寄存器

- □ 单独的端口读 (PS) 和写 (DR) 数据寄存器,能够避免发 生"读操作修改写操作" 错误

- □基于各个引脚的特殊功能

- 仅在 GPIO 引脚上提供的其他特性:

- □ 带 LCD 的器件上的 LCD 段驱动 □ CapSense<sup>[17]</sup>

- □模拟输入和输出功能

- □ 连续 100 µA 钳位电流能力

- □标准驱动强度降至 1.7 V

- 仅在 SIO 引脚上提供的其他功能:

- □ 比 GPIO 更高的驱动强度

- □ 热交换功能 (在任意工作 V<sub>DD</sub> 下容差均为 5 V)

- □ 可编程高电平输入阀值,输出驱动电平低至 1.2 V

- 无模拟输入、 CapSense 或 LCD 功能

- □过压容限高达 5.5 V

- □ SIO 可作为通用模拟电压比较器使用

- USBIO 特性:

- □ 符合 USB 2.0 标准的全速 I/O

- □最大的驱动强度设置可用于一般用途

- □用于 CPU 和 DMA 的输入和 / 或输出

- □ 数字外设的输入和/或输出

- □数字输出 (CMOS) 驱动模式

- □ 每个引脚都可以是一个被配置为上升沿和 / 或下降沿的中断源

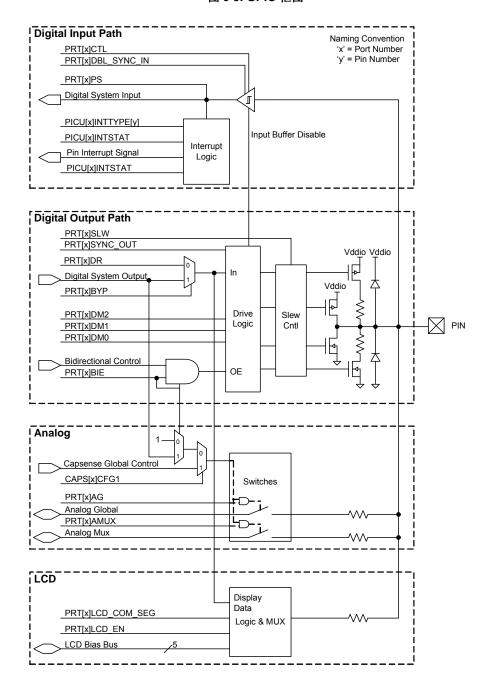

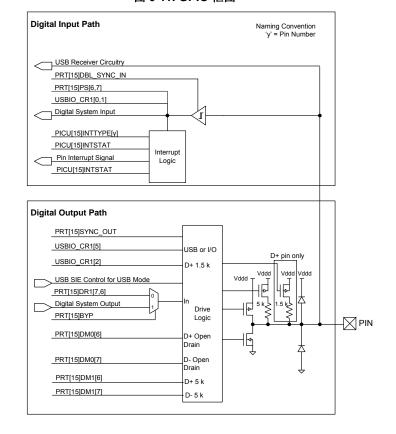

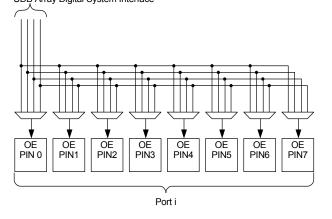

图 6-9. GPIO 框图

Digital Input Path Naming Convention 'x' = Port Number PRT[x]SIO\_HYST\_EN PRT[x]SIO\_DIFF Buffer Thresholds Reference Level PRT[x]DBL\_SYNC\_IN PRT[x]PS Digital System Input PICU[x]INTTYPE[y] Input Buffer Disable PICU[x]INTSTAT Interrupt Pin Interrupt Signal Logic PICU[x]INTSTAT Digital Output Path Reference Level PRT[x]SIO\_CFG PRT[x]SLW Vhigh PRT[x]SYNC\_OUT PRT[x]DR In Digital System Output PRT[x]BYP PRT[x]DM2 Drive Slew PIN PRT[x]DM1 Logic PRT[x]DM0 ┨ **Bidirectional Control** PRT[x]BIE OE

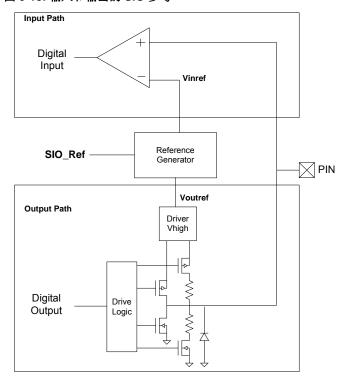

## 图 6-10. SIO 输入/输出框图

图 6-11. GPIO 框图

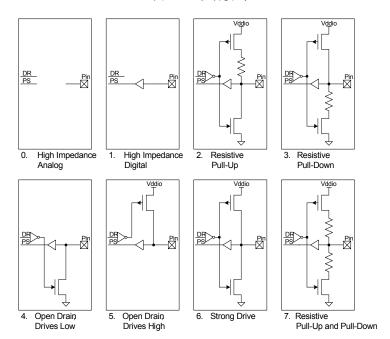

#### 6.4.1 驱动模式

每个 GPIO 和 SIO 引脚都可单独配置成表 6-6 中所列的八种驱动模式中的其中一种。三个配置位可用于每个引脚(DM[2:0]),并在 PRTxDM[2:0] 寄存器中设置。图 6-12 显示了基于每种驱动模式(共八种)的引脚简图。表 6-6 显示了端口数据寄存器值或数字阵列信号(如果选择了旁路模式)对应的 I/O 引脚的驱动状态。请注意,实际的 I/O 引脚电压是由所选驱动模式和引脚负载共同决定的。例如,如果某个 GPIO 引脚被配置为电阻上拉模式,并在引脚悬空时被驱动为高电平,则在引脚处测得的电压会处于高电平的逻辑状态。如果同一个 GPIO 引脚在外部接地,则引脚处未经测量的电压会处于低电平的逻辑状态。

## 图 6-12. 驱动模式

表 6-6. 驱动模式

| 框图 | 驱动模式                      | PRTxDM2 | PRTxDM1 | PRTxDM0 | PRTxDR = 1 | PRTxDR = 0 |

|----|---------------------------|---------|---------|---------|------------|------------|

| 0  | 模拟高阻抗                     | 0       | 0       | 0       | 高阻态        | 高阻态        |

| 1  | 数字高阻抗                     | 0       | 0       | 1       | 高阻态        | 高阻态        |

| 2  | 电阻上拉 [17]                 | 0       | 1       | 0       | 电阻上拉 (5K)  | 强驱动低       |

| 3  | 电阻下拉 [17]                 | 0       | 1       | 1       | 强驱动高       | 电阻下拉 (5K)  |

| 4  | 开漏低驱动                     | 1       | 0       | 0       | 高阻态        | 强驱动低       |

| 5  | 开漏高驱动                     | 1       | 0       | 1       | 强驱动高       | 高阻态        |

| 6  | 强驱动                       | 1       | 1       | 0       | 强驱动高       | 强驱动低       |

| 7  | 电阻上拉 / 下拉 <sup>[17]</sup> | 1       | 1       | 1       | 电阻上拉 (5K)  | 电阻下拉 (5K)  |

#### 注释

17. 在稳压输出模式的 SIO 中不能使用电阻上拉和下拉。

当针对 I/O 模式使能了 USBIO 引脚(P15[7] 和 P15[6])时,会限制驱动模式控制。使用 PRT15.DM0[7, 6] 寄存器设置驱动模式。也可针对 USBIO 引脚选择电阻上拉选项,可使用 PRT15.DM1[7, 6] 寄存器使能此选项。在 USB 模式下使能了驱动模式控制后,不会对 USB 引脚的配置产生影响。与 GPIO 和 SIO 配置不同,端口宽配置寄存器不配置 USB 驱动模式位。表 6-7 显示 USBIO 引脚的驱动模式配置。

## 表 6-7. USBIO 驱动模式 (P15[7] 和 P15[6])

| PRT15.DM1[7,6]<br>上拉电阻被使能 | PRT15.DM0[7,6]<br>驱动模式被使能 | PRT15.DR[7,6] = 1 | PRT15.DR[7,6] = 0 | 说明         |

|---------------------------|---------------------------|-------------------|-------------------|------------|

| 0                         | 0                         | 高阻态               | 强驱动低              | 漏极开路,强驱动低  |

| 0                         | 1                         | 强驱动高              | 强驱动低              | 强输出        |

| 1                         | 0                         | 电阻上拉 (5K)         | 强驱动低              | 电阻上拉, 强驱动低 |

| 1                         | 1                         | 强驱动高              | 强驱动低              | 强输出        |

#### ■高阻抗模拟驱动

默认的复位状态,输出驱动器和数字输入缓冲区均关闭。这可以防止因电压浮动导致任何电流流入到 I/O 的数字输入缓冲区中。对于悬空引脚或支持模拟电压的引脚,建议使用该状态。模拟高阻抗引脚不提供数字输入功能。

要在睡眠模式下最大限度地降低芯片电流,所有 I/O 都必须被配置为模拟高阻抗模式,或通过 PSoC 器件或外部电路将其引脚驱至供电轨。

#### ■ 高阻抗数字驱动

会针对数字信号输入使能输入缓冲区。这是建议用于数字输入 的标准高阻抗(HiZ)状态。

#### ■ 电阻上拉或电阻下拉

电阻上拉或下拉都是在一种数据状态下提供串联电阻,在另一种数据状态下提供强驱动。在这两种模式下,引脚可用于数字输入和输出。这两种模式的一个常见应用是连接机械开关。在稳压输出模式的 SIO 中不能使用电阻上拉和下拉。

■ 开漏驱高 (Open Drain, Drives High)和开漏驱低 (Open Drain, Drives Low)

开漏模式是在一种数据状态下提供高阻抗,在另一种数据状态 下提供强驱动。在这两种模式下,引脚可用于数字输入和输 出。这两种模式的一个常见应用是驱动 I<sup>2</sup>C 总线信号线。

### ■强驱动

无论是在高状态还是低状态,均提供强 CMOS 输出驱动。这是引脚的标准输出模式。一般情况下,采用强驱动模式的引脚不能用作输入。这种模式通常用于驱动数字输出信号或外部FET。

## ■电阻上拉和下拉

与电阻上拉模式和电阻下拉模式类似,只不过引脚始终与电阻 串联。在高数据状态下是上拉,而在低数据状态下是下拉。当 其他可能会导致短路的信号可以驱动总线时,通常会采用此模 式。在稳压输出模式的 SIO 中不能使用电阻上拉和下拉。

#### 6.4.2 引脚寄存器

用于配置引脚并与引脚交互的寄存器有两种形式,并可以互换使 田

所有 I/O 寄存器均可采用标准端口形式,即寄存器的每个位对应于一个端口引脚。这种寄存器形式能够快速有效地同时重新配置 多个端口引脚。

I/O 寄存器也可以采用引脚形式,即针对每个引脚,将八个最常用的端口寄存器位合并到单个寄存器中,以便通过单次寄存器写操作来快速更改各个引脚的配置。

#### 6.4.3 双向模式

借助高速双向功能,引脚可以根据辅助控制总线信号的状态,为输入信号提供高阻抗数字驱动模式,并为同一引脚上的输出信号提供用户选择的另一种驱动模式,例如强驱动(使用PRT×DM[2:0] 寄存器进行设置)。对于需要对输出缓冲区进行动态硬件控制的处理器总线和通信接口,例如 SPI Slave MISO 引脚,双向功能非常有用。

辅助控制总线能够将多达 16 个由 UDB 或数字外设生成的输出使能信号连接至一个或多个引脚。

#### 6.4.4 斜率受限模式

GPIO 和 SIO 引脚针对强驱动和开漏驱动模式提供了快速输出斜率和慢速输出斜率选项(不适用于电阻驱动模式)。由于慢速斜率选项会降低 EMI,因此建议对速度不是很关键(通常小于 1 MHz)的信号使用该选项。快速斜率适用于频率介于 1 MHz 到33 MHz 之间的信号。斜率可以针对每个引脚单独配置,并通过PRT×SLW 寄存器进行设置。

#### 6.4.5 引脚中断

所有 GPIO 和 SIO 引脚都能生成系统中断。每个端口接口上的所有八个引脚均连接到其各自的端口中断控制单元(PICU)及关联的中断向量。端口的每个引脚都可单独配置,以检测上升沿和/或下降沿中断,或不生成中断。

根据为每个引脚配置的模式,每次引脚上发生中断事件时,中断状态寄存器中对应的状态位都会被设为 "1",并且系统会向中断控制器发送中断请求。每个 PICU 在中断控制器和引脚状态寄存器中都有各自的中断向量,以便轻松确定中断源、引脚电平等。

在所有睡眠模式下,端口引脚中断均保持活动状态,以便通过由外部生成的中断唤醒 PSoC 器件。

尽管不直接支持电平敏感中断,但在需要时,可以通过通用数字模块(Universal Digital Block, UDB)为系统提供该功能。

#### 6.4.6 输入缓冲区模式

可以针对默认的 CMOS 输入阈值或可选的 LVTTL 输入阈值在端口级别配置 GPIO 和 SIO 输入缓冲区。所有输入缓冲区都能够与施密特触发器一起实现输入迟滞。此外,在任何驱动模式下,均可禁用各个引脚输入缓冲区。

## 6.4.7 I/O 供电电源

可以提供多达四个 I/O 引脚供电电源,具体取决于器件和封装。每个 I/O 供电电源必须小于或等于芯片模拟(VDDA)引脚的电压。利用此功能,用户可以为器件上的不同引脚提供不同的 I/O 电压电平。要确定给定端口和引脚的 Vddio 功能,请参见特定的器件封装引脚分布图。

SIO 端口引脚支持其他 " 稳压高输出 " 功能,如可调输出电平中所述。

#### 6.4.8 模拟连接

这些连接仅适用于 GPIO 引脚。所有 GPIO 引脚都可以作为模拟输入或输出使用。引脚上的模拟电压不得超过 GPIO 对应的 VDDIO 供电电压。每个 GPIO 都可连接到其中一条模拟全局总线或模拟复用器总线,以便将任意引脚连接到任意内部模拟资源,例如 ADC 或电压比较器。此外,某些引脚能够直接连接到特定的模拟功能,例如大电流 DAC 或运算放大器。

#### 6.4.9 CapSense

本部分内容仅适用于 GPIO 引脚。所有 GPIO 引脚均可用于创建 CapSense 按键和滑动条 <sup>[18]</sup>。有关详细信息,请参考第 61 页上的 CapSense 中介绍的内容。

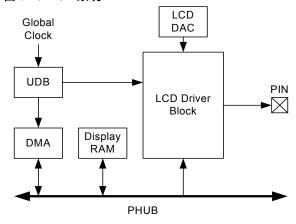

#### 6.4.10 LCD 段驱动

本部分内容仅适用于 GPIO 引脚。所有 GPIO 引脚均可用于生成段驱动和共模驱动信号,以便直接驱动 LCD 显示屏。有关详细信息,请参考第 60 页上的 LCD 直接驱动器中介绍的内容。

## 6.4.11 可调输出电平

本部分内容仅适用于 SIO 引脚。 SIO 端口引脚支持为电压低于 SIO 对应 VDDIO 的外部信号接口提供经稳压的高电平输出。根据内部生成的参考电压,各个 SIO 引脚可单独配置为标准 VDDIO 电平输出或稳压输出。通常会使用电压 DAC (VDAC)来生成参考电压(请参见图 6-13)。第 62 页上的 DAC 详细介绍了 VDAC 的用法以及如何将参考电压连接至 SIO 引脚。电阻上拉和下拉驱动模式不适用于稳压输出模式下的 SIO。

#### 注释

18. Opamp 的固有输出引脚不建议用作 CapSense 功能。

#### 6.4.12 可调输入电平

本部分内容仅适用于 SIO 引脚。默认情况下,SIO 引脚不仅支持标准 CMOS 和 LVTTL 输入电平,而且还支持采用可编程电平的差分模式。SIO 引脚按对分组。每对引脚共享一个参考电压发生器模块,该模块用于为电压与 VDDIO 不同的外部信号接口设置数字输入缓冲区参考电平。参考电压会用来设置高逻辑电平的引脚电压阈值(请参见图 6-13)。可用的输入阈值包括:

- 0.5 × VDDIO

- 0.4 × VDDIO

- 0.5 × V<sub>REF</sub>

- V<sub>REF</sub>

通常会使用电压 DAC(VDAC)来生成  $V_{REF}$  参考电压。第 62 页上的 DAC 详细介绍了 VDAC 的用法以及连接至 SIO 引脚的参考电压。

#### 图 6-13. 输入和输出的 SIO 参考

#### 6.4.13 SIO 作为电压比较器

本部分内容仅适用于 SIO 引脚。如可调输入电平一节所述,可以使用 SIO 的可调输入电平功能来构建电压比较器。电压比较器的阈值由 SIO 的参考电平发生器提供。参考电平发生器包含一个用于将通过模拟全局总线连接的模拟信号设为电压比较器阈值的选项。请注意,一对 SIO 引脚共享同一个阈值。

第 37 页上的图 6-10 中的数字输入路径阐释了此功能。在该图中,"参考电平"是通过模拟全局总线连接过来的模拟信号。还可以为 SIO 的输入缓冲区使能迟滞功能,以便增强电压比较器的抗噪能力。

#### 6.4.14 热插拔

本部分内容仅适用于 SIO 引脚。SIO 引脚支持 "热插拔" 功能,无需加载连接到 SIO 引脚的信号即可插入到应用中,即便在 PSoC 器件未通电时亦是如此。这样一来,未通电的 PSoC 就可以保持对外部器件的高阻抗负载,同时防止 PSoC 被通过 SIO 引脚的保护二极管的电流加电。

与正在运行的 I2C 总线相连时,给该器件供电或断电会导致 SIO 引脚上的瞬变状态。 I2C 总线的整体设计应该考虑这一点。

#### 6.4.15 过压容限

所有 I/O 引脚在任意工作 V<sub>DD</sub> 下都能够提供过压容差功能。

- SIO 引脚没有电流限制,因为它们对外部电路存在高阻抗负载, 其中 VDDIO ≤ V<sub>IN</sub> ≤ 5.5 V。

- GPIO引脚电流必须使用限流电阻限制为100 µA。GPIO引脚会钳制引脚电压约为 VDDIO 加一个二极管电压,其中 VDDIO≤ VIN ≤ VDDA。

- 如果 GPIO 引脚被配置为用于模拟输入/输出,则引脚上的模拟 电压不得超过 GPIO 对应的 VDDIO 供电电压。

此功能的一个常见应用是连接到  $I^2C$  等总线,其中不同的器件在不同的供电电压下运行。连接到  $I^2C$  时,会针对 SIO 引脚将 PSoC 芯片配置为开漏驱低(Open Drain、Drives Low)模式。这样就可以通过外部上拉电阻将  $I^2C$  总线电压拉到 PSoC 引脚供电电压以上。例如, PSoC 芯片可以在 1.8 V 下运行,外部器件可以在 5 V 下运行。请注意,SIO 引脚的  $V_{IH}$  和  $V_{IL}$  电平由关联的 Vddio 供电引脚决定。

SIO 引脚必须处于下列模式之一: 0 (模拟高阻抗)、1 (数字高阻抗)或4 (开漏驱动低电平)。有关详细信息,请参考图 6-12中介绍的内容。必须针对所有 I/O 引脚监控器件的绝对最大额定值。

## 6.4.16 复位配置

当复位有效时,所有 I/O 都会复位并保持在模拟高阻抗状态。复位释放之后,可根据各个端口将状态重新编程为下拉或上拉。为了确保正确的复位操作,端口复位配置数据会存储在专用的非易失性寄存器中。发出复位信号后,存储的复位数据会自动传输到端口复位配置寄存器。

## 6.4.17 低功耗功能

在所有低功耗模式下, I/O 引脚都会保持其状态,直到部件被唤醒并被更改或复位。要唤醒部件,请使用引脚中断,因为在所有低功耗模式下,端口中断逻辑会继续发挥作用。

## 6.4.18 特殊引脚功能

器件上的某些引脚除了具有 GPIO 或 SIO 功能以外,还具有其他特殊功能。第 6 页上的引脚分布中列出了具体的特殊功能引脚。这些特殊功能包括:

## ■数字

- □ 4 至 25 MHz 晶振

- □ 32.768 kHz 晶振

- □ JTAG 接口引脚

- □ SWD 接口引脚

- □SWV 接口引脚

- □外部复位

- 模羽

- □运算放大器输入和输出

- □ 大电流 IDAC 输出

- □外部参考输入

## 6.4.19 JTAG 边界扫描

器件支持所有 I/O 引脚上的标准 JTAG 边界扫描链,以便进行板级测试。

# 7. 数字子系统

可编程数字系统能够针对应用创建标准数字外设、高级数字外设 与定制逻辑功能的组合。这些外设和逻辑随后将互连,并与器件 上的任意引脚相连,从而提供高度的设计灵活性和 IP 安全性。

下面列出了可编程数字系统的功能,以便用户对这些功能和架构有一个大概的了解。设计人员不需要在硬件和寄存器级别同可编程数字系统直接交互。PSoC Creator 提供了一个与 PLD 类似的高级电路图输入图形界面,以便自动放置和连接资源。

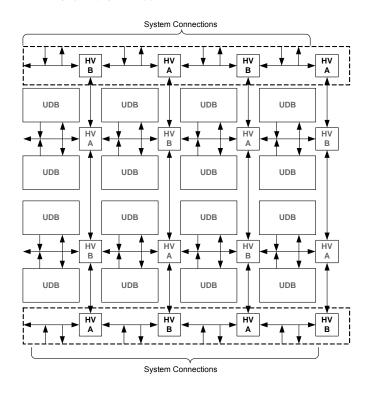

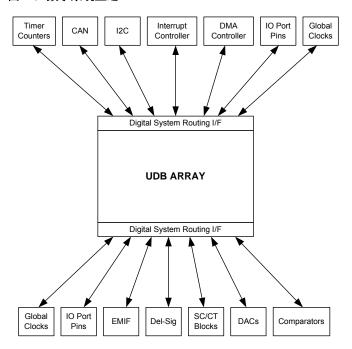

可编程数字系统的主要组件包括:

- ■通用数字模块(UDB)— 这些模块构成了可编程数字系统的核心功能。UDB是未赋定逻辑(PLD)和结构化逻辑(数据路径)的组合,已经过优化,能够针对应用或设计创建所有常用嵌入式外设和定制功能。

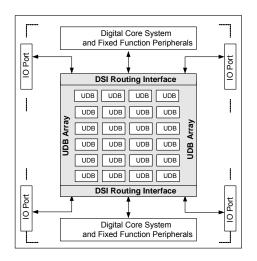

- 通用数字模块阵列 UDB 模块排列在一个可编程互连矩阵内。UDB 阵列结构具有一致性,有助于将数字功能灵活地映射到阵列上。该阵列支持在 UDB 与数字系统互连之间进行广泛而灵活的布线互连。

- ■数字系统互连(DSI)— 来自通用数字模块(UDB)、固定功能外设、I/O 引脚、中断和 DMA 的信号以及其他系统内核信号会连接到数字系统互连,以实现全功能器件连通性。与通用数字模块阵列(Universal Digital Block Array)结合使用时,DSI允许将任意数字功能连接至任意引脚或其他组件。

## 图 7-1. CY8C36 可编程数字架构

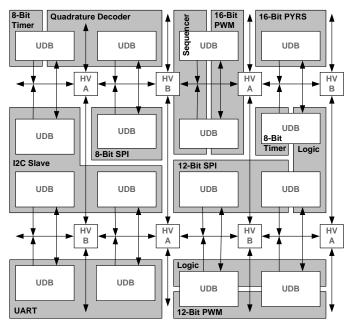

## 7.1 外设示例

CY8C36 系列的通用数字模块(UDB)和模拟模块具有高度的灵活性,可以支持用户创建许多组件(外设)。赛普拉斯开发了一些最常用的外设,具体请参考 PSoC Creator 组件目录。此外,用户还可以使用 PSoC Creator 创建自己的定制组件。利用 PSoC Creator,用户还可以创建自己的组件,以便在其组织内重复使用,例如传感器接口、专有算法,以及显示界面。

PSoC Creator 提供了大量的组件,我们无法在数据手册中一一列出,而且这些组件的数量还在不断增加。例如, UART 组件可用于 CY8C36 系列但未在本数据手册中提到。

## 7.1.1 数字组件示例

以下是可用于 CY8C36 系列的 PSoC Creator 的一个数字组件采样。组件使用的硬件资源(UDB、布线、 RAM、闪存)的确切数量会有所不同,具体取决于在 PSoC Creator 中为组件选择的功能。

- ■通信

- □ I<sup>2</sup>C

- □ UART

- □ SPI

- ■函数

- EMIF

- □ PWM

- □定时器

- □计数器

- ■逻辑

- NOT

- □ OR

- XOR

- AND

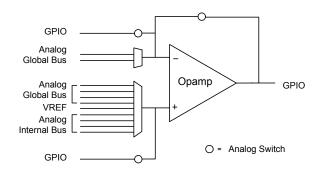

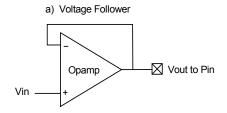

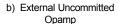

## 7.1.2 模拟组件示例

以下是可用于 CY8C36 系列的 PSoC Creator 的一个模拟组件采样。组件使用的硬件资源(SC/CT 模块、布线、 RAM、闪存)的确切数量会有所不同,具体取决于在 PSoC Creator 中为组件选择的功能。

- ■放大器

- □ TIA

- □ PGA

- opamp

- ADC

- Delta-Sigma

- DAC

- □电流

- □电压

- □ PWM

- ■电压比较器

- 混频器

## 7.1.3 系统功能组件示例

以下是可用于 CY8C36 系列的 PSoC Creator 的一个系统功能组件采样。组件使用的硬件资源(UDB、DFB 抽头、SC/CT 模块、布线、RAM、闪存)的确切数量会有所不同,具体取决于在 PSoC Creator 中为组件选择的功能。

- CapSense

- LCD 驱动

- LCD 控制

- ■滤波器

## 7.1.4 使用 PSoC Creator 进行设计

## 7.1.4.1 优于典型 IDE

一个成功的设计工具应该能够快速开发并部署简单的和复杂的设计,缩短甚至消除学习过程,并使新设计直接融入到生产流程中。

PSoC Creator 就是这样的设计工具。

PSoC Creator 是一个功能齐全的集成开发环境(IDE),可用于硬件和软件的设计。该工具已针对 PSoC 器件进行优化,并将功能强大的新型软件开发平台与先进的图形化设计工具结合在一起。这种独特的工具组合使得 PSoC Creator 成为目前灵活性最高的嵌入式设计平台。

图形化设计输入有助于简化特定部件的配置。您可以从内容丰富的组件目录中选择所需的功能,并将其放入到自己的设计中。所有组件都实现了参数化,并具有编辑器对话框,您可以根据自己的需求来定制功能。

PSoC Creator 会自动配置时钟,并将 I/O 连接至选定的引脚,随后生成 API,以便应用程序能够对硬件进行全面控制。要更改 PSoC 器件配置,只需添加一个新组件,设置其参数并重建项目即可。

在开发过程的任何阶段,您都可以自由更改硬件配置乃至目标处理器。要将应用(硬件和软件)重新定位到新器件(即使是从8位系列到32位系列),只需选择新器件并重建即可。

您还可以更改 C 编译器并评估备选方案。组件具有高度的便携性,并针对所有系列的所有器件以及支持的所有工具链进行了验证。要切换编译器,只需编辑项目选项,并使用生成的 API 或引导代码正确地重建应用即可。

### 7.1.4.2 组件目录

组件目录是一个由可重复使用的设计元素组成的资料库,能够帮助您选择器件功能并定制 PSoC 器件。组件目录中包含大量实用的内容:从简单的基元(例如逻辑门和器件寄存器),到数字定时器、计数器和 PWM,再到模拟组件(例如 ADC、 DAC 和滤波器)以及通信协议(例如 I<sup>2</sup>C、USB 和 CAN),应有尽有。有关可用外设的更多详细信息,请参考第 41 页上的外设示例中介绍的内容。所有内容均已完全特性表征化,并在数据手册中进行了详细记录,同时附有代码示例、交流 / 直流规范以及已编好用户代码的 API。

## 7.1.4.3 设计重复使用

符号编辑器可让您开发能够重复使用的组件,从而大大缩短日后进行设计所需的时间。您只需绘制符号,并将其与经过验证的设计相关联即可。PSoC Creator允许将新符号与赛普拉斯提供的内容一起放在组件目录中的任意位置。然后,您就可以在任意数量的项目中不限次数地重复使用您的内容,而无需重复查看其详细的实现信息。

## 7.1.4.4 软件开发

该工具拥有时尚且高度可定制的用户界面。它不仅包括项目管理功能以及适用于 C 语言和汇编语言源代码的集成编辑器,而且还包括设计输入工具。

项目构建控制功能采用了由 ARM® Limited、Keil™和 CodeSourcery (GNU)等顶级商业供应商所提供的编译器技术。该工具随附有适用于 ARM 的免费版 Keil C51 和 GNU C编译器(GCC),这些编译器对代码规模或最终产品分发没有任何限制。该工具支持专业的 Keil C51 产品和 ARM RealView™ 编译器,能够轻松升级到更多优化编译器。

## 7.1.4.5 非侵入式调试

由于所有器件均提供 JTAG(4线)和 SWD(2线)调试连接,因此 PSoC Creator 调试器只需很少的干预,即可全面控制目标器件。断点和代码执行命令都可通过工具栏按键直接调用,一系

列实用的窗口 (寄存器、局部、监控、调用堆栈、存储器和外设) 有助于实现无与伦比的系统可视性。

PSoC Creator 包含完成设计,以及日后维护和扩展设计所需的所有工具。设计流程的所有步骤都经过了仔细整合和优化,不仅简单易用,而且能最大限度地提高效率。

#### 7.2 通用数字模块

通用数字模块(UDB)标志着向下一代 PSoC 嵌入式数字外设功能迈出了具有革命性意义的一步。第一代 PSoC 数字模块的架构提供了粗糙的可编程性,其中仅包含一些具有少量选项的固定功能。新型 UDB 架构在配置精细程度和高效实现两者之间取得了最佳平衡。此方法的核心是提供根据应用需求定制器件数字操作的能力。

为了实现这一点,UDB 包含了未赋定逻辑(PLD)、结构化逻辑(数据路径)与灵活布线方案的组合,以便在这些元素、I/O 连接以及其他外设之间提供互连能力。UDB 具有丰富的功能,从在一个 UDB 甚至是 UDB 的一部分(未使用的资源可供其他功能使用)中实现的简单自包含功能,到需要多个 UDB 的更为复杂的功能,应有尽有。基本函数的示例为定时器、计数器、CRC 发生器、PWM、死区发生器和通信函数如 UART、SPI 和 I<sup>2</sup>C。另外,PLD 模块和连接在可用的资源上提供功能齐全的通用可编程逻辑。

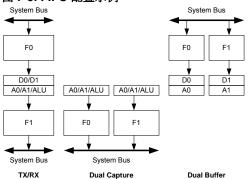

#### 图 7-2. UDB 框图

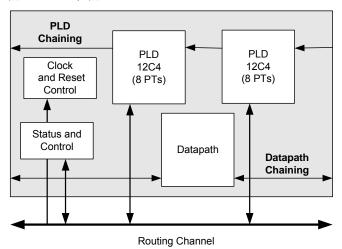

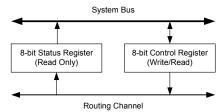

UDB 的主要组件模块包括:

- PLD模块 每个UDB有两个小型PLD。这些模块从连接阵列获取输入,并构成寄存或组合 " 乘积和 " 逻辑。PLD 用于实现状态机、状态位和组合逻辑方程。PLD 配置是从图元自动生成的。

- ■数据路径模块——这一8位宽的数据路径包含结构化逻辑,能够实现可动态配置的 ALU、各种比较配置,以及条件生成。该模块还包含输入/输出 FIFO,这些 FIFO 是 CPU/DMA 系统与UDB 之间的主要并行数据接口。

- ■状态和控制模块 该模块的主要作用是为 CPU 固件提供与 UDB 操作进行交互和同步的方式。

■时钟和复位模块 — 该模块能够提供 UDB 时钟以及复位选择和控制功能。

## 7.2.1 PLD 模块

PLD 模块的主要用途是实现逻辑表达式、状态机、序列发生器、查询表和解码器。在最简单的使用模型中,可将 PLD 模块视为单独的资源,通用 RTL 会综合并映射到此资源。更为常见且有效的使用模型是通过组合使用 PLD 和数据路径模块创建数字功能。其中,PLD仅实现功能的随机逻辑和状态部分,而数据路径(ALU)则实现更多结构化元素。

## 图 7-3. PLD 12C4 结构

图 7-3 显示的是一个 12C4 PLD 模块。此 PLD 的 12 个输入能够带动八个乘积项。每个乘积项(AND 功能)的宽度可以是 1 到 12 个输入,并且在给定的乘积项中,可以选择每个输入的真值(T)或补码(C)。对乘积项求和(OR 功能)即可创建 PLD 输出。总和的宽度可以是 1 到 8 个乘积项。12C4 中的 "C"表示OR门的宽度(在本例中为 8) 在所有输出中都不变(而在 22V10器件中是可变的)。这种类似于 PLA 的结构能够实现最大的灵活性,并确保所有输入和输出都是可交换的,以便通过软件工具轻松地进行分配。每个 UDB 中有两个 12C4 PLD。

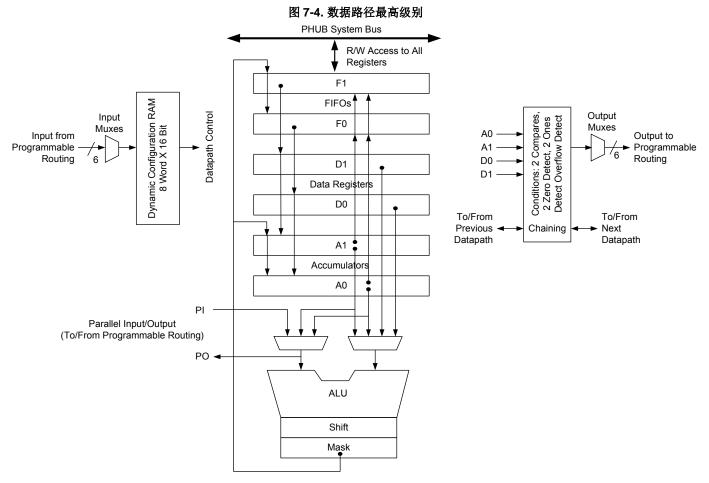

#### 7.2.2 数据路径模块

数据路径包含一个8位的单周期ALU,并具有关联的比较和条件生成逻辑。此数据路径模块经过了优化,能够实现嵌入式功能,如定时器、计数器、积分器、PWM、PRS、CRC、移位器、死区生成器等。

## 7.2.2.1 工作寄存器

数据路径包含六个主要工作寄存器,在正常操作的期间可通过 CPU 固件或 DMA 访问这些寄存器。

## 表 7-1. 工作数据路径寄存器

| 名称      | 功能    | 说明                                                                   |

|---------|-------|----------------------------------------------------------------------|

| A0 和 A1 | 累加器   | 这些寄存器是 ALU 的源和库<br>(sink), 也是比较器的源。                                  |

| D0 和 D1 | 数据寄存器 | 这些寄存器是 ALU 的源,也是<br>比较器的源。                                           |

| F0 和 F1 | FIFO  | 这些寄存器是系统总线的主要接口。它们可以是数据寄存器和累加器的数据源,或者从累加器或ALU 捕获数据。每个 FIFO 的深度为四个字节。 |

## 7.2.2.2 动态数据路径配置 RAM

动态配置指的是在序列发生器的控制下,按周期更改数据路径功能和内部配置的能力。这是使用8字×位配置RAM实现的,该RAM存储有八个具有唯一性的16位宽配置。此RAM的地址输

入用于控制序列,可以来自与 UDB 布线矩阵相连的任何模块(最典型的是 PLD 逻辑、 I/O 引脚),或来自此数据路径模块或其他数据路径模块的输出。

#### ALU

ALU 能够执行八种通用功能,其中包括:

- ■递增

- ■递减

- ■加

- ■减

- ■逻辑 AND

- ■逻辑 OR

- ■逻辑 XOR

- 传输,用于通过 ALU 将某值传输到移位寄存器、掩码寄存器或 其他 UDB 寄存器

除了 ALU 运算之外,还能够提供以下功能:

- 向左移位

- ■向右移位

- ■半字节交换

文档编号: 001-92989 版本 \*A

#### ■ 按位 OR 掩码

#### 7.2.2.3 条件

每个数据路径包含两个比较操作,并具有位掩码选项。比较操作数包括由两个累加器和两个数据寄存器组成的各种配置。其他条件包括零检测、全一检测和溢出。这些条件是主要的数据路径输出,其中有些可输出到 UDB 走线矩阵中。条件计算可以使用连接到相邻 UDB 的内置链路,以在较宽的数据宽度上进行运算,而无需使用走线资源。

## 7.2.2.4 *变量 MSB*

算术和移位功能的最高有效位可通过编程方式指定。变量 MSB 支持可变宽度 CRC 和 PRS 功能,而且通过与 ALU 输出掩码相结合,可实现任意宽度的定时器、计数器和移位模块。

#### 7.2.2.5 内置 CRC/PRS

数据路径包含对以下内容的内置支持:任意宽度和任意多项式的单周期 CRC 计算和 PRS 生成。长度超过 8 位的 CRC/PRS 功能可通过结合使用 PLD 逻辑来实现,而内置链路可用于将该功能扩展至相邻 UDB。

#### 7.2.2.6 输入/输出 FIFO

每个数据路径包含两个 4 字节深的 FIFO,这些 FIFO 可单独配置为输入缓冲区(系统总线写入到 FIFO,数据路径内部读取 FIFO)或输出缓冲区(数据路径内部写入到 FIFO,系统总线读取 FIFO)。FIFO能够生成状态,这些状态可被选为数据路径输出,从而可连接至走线,以便与序列发生器、中断或 DMA 进行交互。

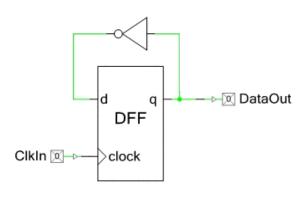

## 图 7-5. FIFO 配置示例

# 7.2.2.7 链路

数据路径可被配置为将条件和信号(例如进位和移位数据)同相 邻数据路径进行链接,以便创建准确度更高的算术、移位和 CRC/PRS 功能。

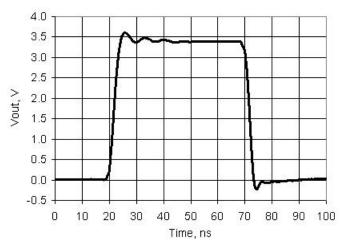

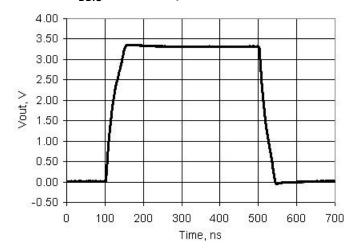

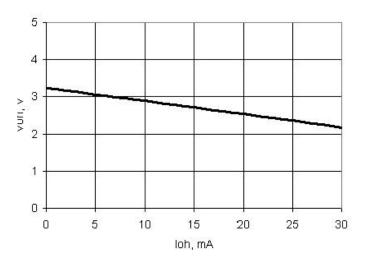

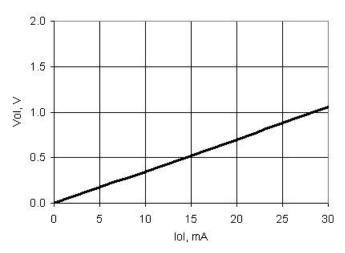

### 7.2.2.8 时间复用