- ASIC

- 电池管理 IC

- 时钟和时序解决方案

- ESD 和浪涌保护器件

- 汽车以太网

- 评估板

- 高可靠性

- 隔离

- 存储器

- 微控制器

- 功率产品

- 射频

- 安全智能卡解决方案

- 传感器技术

- 小信号晶体管和二极管

- 收发器

- 通用串行总线(USB)

- 无线连接

- 英飞凌大中华区生态圈

- 搜索工具

- 技术

- 封装

- 订单

- 概览

- 嵌入式闪存eFlash IP 解决方案

- RAM和Flash多芯片封装MCP解决方案

- F-RAM铁电存储器

- NOR 闪存

- nvsRAM非易失性存储器

- PSRAM — 伪静态RAM

- 抗辐射和高可靠性的存储器

- SRAM静态随机存储器

- 晶圆和裸片存储器解决方案

- 概览

- AC-DC电源转换

- 电动汽车动力系统

- D 类音频放大器 IC

- 非接触式电源和检测 IC

- DC-DC 转换器

- 二极管&晶闸管 (Si/SiC)

- 氮化镓(GaN)

- GaN EiceDRIVER™高速栅极驱动器

- IGBT 产品及驱动器件

- 智能功率模块(IPM)

- LED 驱动芯片

- 电动机驱动器

- MOSFET

- 功率模块

- 电源模块

- 保护和监控IC

- 碳化硅 (SiC)

- 智能电源开关

- 固态继电器

- 无线充电 IC

- 概览

- Calypso® 产品

- CIPURSE™ 产品

- 非接触式存储

- 了解 OPTIGA™ 嵌入式加密解决方案

- SECORA™ 安全解决方案

- 安全控制器

- 智能卡模块

- 政府身份证的智能解决方案

- 概览

- USB 2.0 外设控制器

- USB 3.2 外设控制器

- USB 集线器控制器

- USB PD 高压微控制器

- USB-C AC-DC 和 DC-DC 充电解决方案

- USB-C 充电端口控制器

- USB-C 供电控制器

- 概览

- AIROC™ 车载无线

- AIROC™ 蓝牙Bluetooth® 和多协议解决方案

- AIROC™ 互联微控制器

- AIROC™ Wi-Fi + Bluetooth® 组合

- 概览

- FM0+ 32 位 Arm® Cortex-M0®+ 微控制器 (MCU) 系列

-

FM3 32 位 Arm® Cortex-M3® 微控制器 (MCU) 系列

- 概览

- FM3 CY9AFx1xK 系列 Arm® Cortex-M3® 微控制器 (MCU)

- FM3 CY9AFx1xL/M/N 系列 Arm® Cortex-M3® 微控制器 (MCU)

- FM3 CY9AFx2xK/L 系列 Arm® Cortex-M3® 微控制器 (MCU)

- FM3 CY9AFx3xK/L 系列超低漏电流 Arm® Cortex-M3® 微控制器 (MCU)

- FM3 CY9AFx4xL/M/N 系列低功耗 Arm® Cortex-M3® 微控制器 (MCU)

- FM3 CY9AFx5xM/N/R 系列低功耗 Arm® Cortex-M3® 微控制器 (MCU)

- FM3 CY9AFxAxL/M/N 系列超低漏电流 Arm® Cortex-M3® 微控制器 (MCU)

- FM3 CY9BFx1xN/R 高性能系列 Arm® Cortex-M3® 微控制器 (MCU)

- FM3 CY9BFx1xS/T 高性能系列 Arm® Cortex-M3® 微控制器 (MCU)

- FM3 CY9BFx2xJ 系列 Arm® Cortex-M3®微控制器 (MCU)

- FM3 CY9BFx2xK/L/M 系列 Arm® Cortex-M3® 微控制器 (MCU)

- FM3 CY9BFx2xS/T 系列 Arm® Cortex-M3® 微控制器 (MCU)

- FM4 32 位 Arm® Cortex-M4® 微控制器 (MCU) 系列

- 概览

-

TriCore™ AURIX™ TC2x安全模块

- 概览

- AURIX™系列 – TC21xL

- AURIX™ 系列 – TC21xSC (无线充电)

- AURIX™ 系列 – TC22xL

- AURIX™系列 – TC23xL

- AURIX™ 系列 – TC23xLA (ADAS)

- AURIX™ 系列 – TC23xLX

- AURIX™ 系列 – TC264DA (ADAS)

- AURIX™系列 – TC26xD

- AURIX™ 系列 – TC27xT

- AURIX™ 系列 – TC297TA (ADAS)

- AURIX™ 系列 – TC29xT

- AURIX™ 系列 – TC29xTT (ADAS)

- AURIX™系列 – TC29xTX

- AURIX™ TC2x仿真器件

- 32 位TriCore™ AURIX™ – TC3x

- 32 位TriCore™ AURIX™ - TC4x

- 概览

- PSOC™ 4 Arm® Cortex® -M0/M0+

- PSOC™ 4 HV Arm® Cortex® -M0+

- PSOC™ 5 LP Arm® Cortex® -M3

- PSOC™ 6 Arm® Cortex-M4®/M0+

- PSOC™ 多点触控触摸屏控制器

- PSOC™ Control C3 Arm® Cortex®-M33

- PSOC™ Automotive 4: Arm® Cortex®-M0/M0+

- PSOC™ Edge Arm® Cortex® M55/M33

- 概览

- 32 位 TRAVEO™ T2G Arm® Cortex®用于车身电子应用

- 用于仪表盘的 32 位 TRAVEO™ T2G Arm® Cortex®

- 概览

- 32 位XMC1000工业微控制器 Arm® Cortex-M0®

- 32 位XMC4000工业微控制器 Arm® Cortex-M4®

- XMC5000 Industrial Microcontroller Arm® Cortex®-M4F

- 32 位XMC7000工业微控制器 Arm® Cortex-M7®

- 概览

- 桥式整流器和交流开关

- CoolSiC™ 肖特基二极管

- 二极管裸片

- 硅二极管

- 晶闸管/二极管模块

- 晶闸管软启动器模块

- 晶闸管/二极管盘

- 概览

- BLDC 电机驱动器

- BDC电机驱动器

- 步进电机和伺服电机驱动器

- 带MCU的电机驱动器

- 使用 MOSFET 的桥式驱动器

- GaN EiceDRIVER™高速栅极驱动器

- 概览

- 汽车级MOSFET

- 双 MOSFET

- MOSFET(Si 和 SiC)模块

- N 沟道耗尽型 MOSFET

- N 沟道 MOSFET

- P 沟道 MOSFET

- 碳化硅 CoolSiC™ MOSFET

- 250V至600V G14小信号MOS

- 概览

- OPTIGA™ Authenticate

- OPTIGA™ Authenticate NFC 解决方案

- OPTIGA™ Connect – 交钥匙式 eSIM 安全解决方案

- OPTIGA™ Trust

- OPTIGA™ 可信平台模块 (TPM)

- 概览

- EZ-PD™ ACG1F 单端口 USB-C 控制器

- EZ-PD™ CCG2 USB Type-C 端口控制器

- EZ-PD™ CCG3PA Automotive USB-C 和 Power Delivery 控制器

- EZ-PD™ CCG4 双端口 USB-C 和 PD

- EZ-PD™ CCG5 双端口和 CCG5C 单端口 USB-C PD 控制器

- EZ-PD™ CCG6 单端口 USB-C & PD 控制器

- EZ-PD ™ CCG6_CFP 和 EZ-PD ™ CCG8_CFP 双单端口 USB-C PD

- EZ-PD™ CCG6DF 双端口和 CCG6SF 单端口 USB-C PD 控制器

- EZ-PD™ CCG7D 汽车双口 USB-C PD + DC-DC 控制器

- EZ-PD™ CCG7S 汽车单口 USB-C PD 解决方案,配备DC-DC控制器

- EZ-PD™ CCG8 双/单口 USB-C PD

- EZ-PD™ CMG1 USB-C EMCA 控制器

- 支持 EPR 的 EZ-PD™ CMG2 USB-C EMCA 控制器

- 最新动态

- 航空航天

- 人工智能和数据中心

- 智能汽车解决方案

- 通讯

- 消费类电子产品

- 健康和 生活方式

- 家用电器

- 工业

- 可再生能源

- 机器人

- 安全解决方案

- 智能家居和楼宇

- 解决方案

- 概览

- 电源适配器和充电器

- 适用于智能电视的完整系统解决方案

- 移动设备和智能手机解决方案

- 多旋翼飞机和无人机

- 电动工具

- 家庭娱乐应用的半导体解决方案

- 智能会议系统

- 概览

- 电池化成和测试

- 电动汽车充电

- 氢气

- 光伏

- Wind power

- Solid-state circuit breaker (SSCB)

- Battery energy storage (BESS)

- 概览

- 汽车辅助系统

- 车载网关

- 汽车pds配电系统

- 车身控制模块 (BCM)

- 舒适便捷电子产品

- 区域 DC-DC 转换器 48 V-12 V

- 区域控制器

- 最新动态

- 概览

- AIROC™ 软件&工具

- AURIX™应用软件

- DRIVECORE 用于汽车软件开发

- iMOTION™ 工具和软件

- Infineon智能功率开关和栅极驱动器工具套件

- MOTIX 软件&工具

- OPTIGA™工具和软件

- PSOC™ 软件&工具

- TRAVEO™ 软件&工具

- XENSIV™ 工具和软件

- XMC™ 工具和软件

- 概览

- EZ-PD™ CCGx Dock 软件开发工具包

- FMx Softune IDE

- ModusToolbox™ 软件

- PSOC™ Creator软件

- 雷达开发套件

- 锈

- USB 集线器控制器

- 无线连接蓝牙网状网络辅助应用程序

- XMC™ DAVE™ 软件

- 最新动态

- 支持

- 培训

- 英飞凌开发者社区

- 最新消息

商业财经新闻

15/04/2026

商业财经新闻

13/04/2026

商业财经新闻

24/03/2026

商业财经新闻

16/03/2026

- 公司名称

- 我们的故事

- 活动资讯

- 新闻中心

- 投资者

- 职业生涯

- 质量

- 最新消息

商业财经新闻

15/04/2026

商业财经新闻

13/04/2026

商业财经新闻

24/03/2026

商业财经新闻

16/03/2026

这是机器翻译的内容,点击这里了解更多

AURIX™ - XILINX FPGA 链路

利用优化的AURIX™ -XILINX FPGA 连接最大程度提高性能

-

在本页

关于

英飞凌科技股份公司、赛灵思公司和Xylon , doo合作以便在汽车和工业应用中更灵活地使用安全微控制器。Xylon 的全新 IP 核可通过英飞凌高速串行链路 (HSSL) 实现英飞凌 AURIX 系列微控制器( TC2xx和TC3xx )与 Xilinx SoC(片上系统)、MPSoC(多处理器 SoC)和 FPGA(现场可编程门阵列)设备之间的高速通信。该串行链路支持高达 320 Mbaud 的波特率,净有效载荷数据率高达 84%。

新的 IP 核将允许系统开发人员将AURIX™提供的功能安全性和安全性与 Xilinx 设备带来的广泛功能可能性结合起来。 链接的设备可以通过 HSSL 访问和控制彼此的内部和连接资源。

- 目前支持 Xilinx 7 系列和 Zynq-7000 SoC 设备系列

- 计划在不久的将来支持 Xilinx UltraScale、UltraScale+ FPGA 设备和 Zynq UltraScale+ MPSoC。

- HSSL从属设备

- 波特率高达 320 Mbaud/s

- 符合 ARM AMBA AXI4-Lite 总线协议,可作为从属设备

- 符合 ARM AMBA AXI4 总线协议的主设备

- 3.25 GB 的可寻址空间涵盖以下访问:

- FPGA 结构寄存器和 RAM

- PS 部分寄存器空间和 OCM

- 板载线性可寻址 FLASH 设备

- 板载 DDR 内存

套件描述

logiHSSL-ZU FPGA HSSL 入门套件 设计为系统设计人员提供了所需的一切,以便通过英飞凌高速串行链路 ( HSSLAURIX™ ) 快速将英飞凌的 微控制器与 Xilinx 全可编程 FPGA 和 SoC 设备互连。这些设备的组合解决了新兴汽车和工业设计中日益增长的安全性和性能要求。

套件内容

- 结合英飞凌的AURIX™微控制器和赛灵思的 UltraScale+ MPSoC 可编程设备

- 集成针对 Xilinx FPGA 实现优化的英飞凌高速串行链路 ( HSSL )

- 包含带有评估logiHSSL IP 核的完整参考设计

- 设计已为 Xilinx Vivado ®设计套件做好准备

- 链接的设备可以访问和控制彼此的资源

- 完整的硬件平台包括:

- 1 个 Xilinx Zynq UltraScale+ MPSoC ZCU104 评估套件

- 1x 英飞凌 Aurix 评估板套件KIT_A2G_TC397_5V_TRB_S

- 1 个 Xylon FMC 板用于电缆连接

1根FireWire线缆

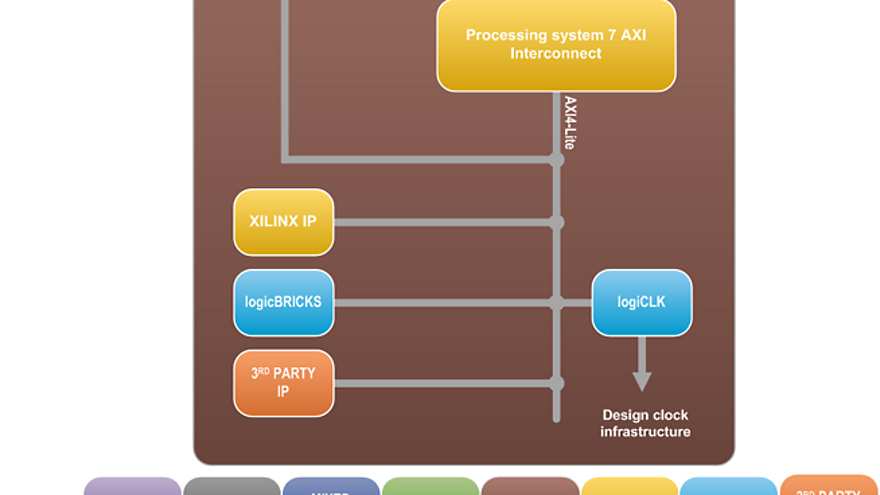

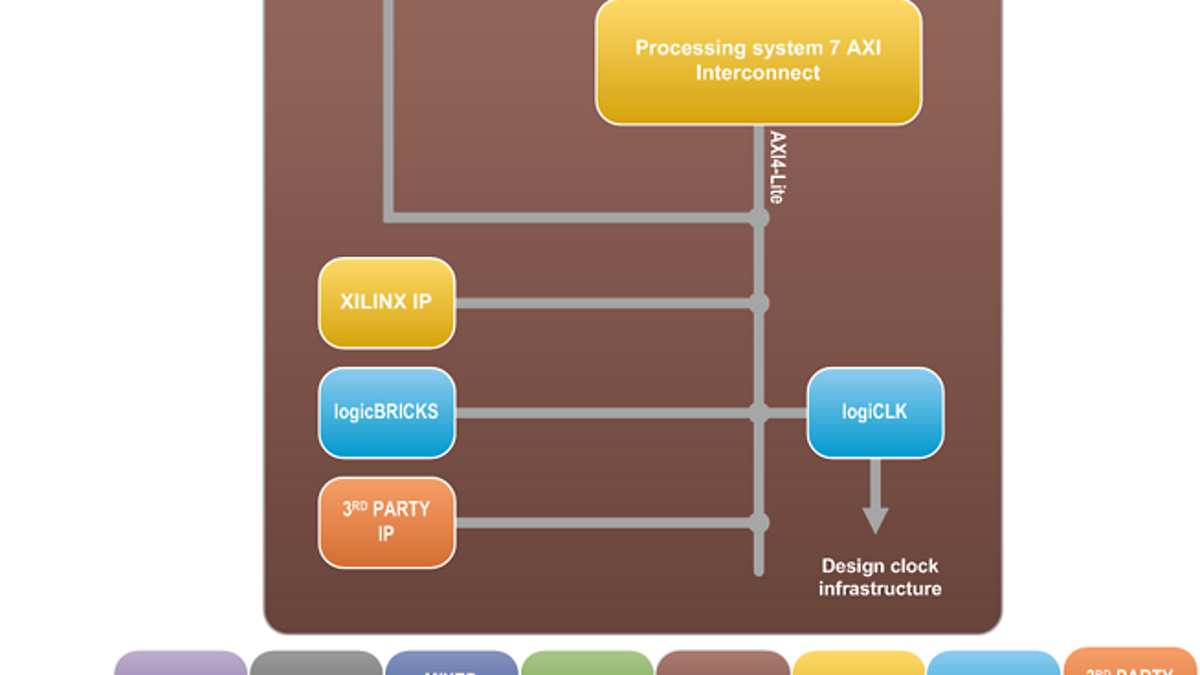

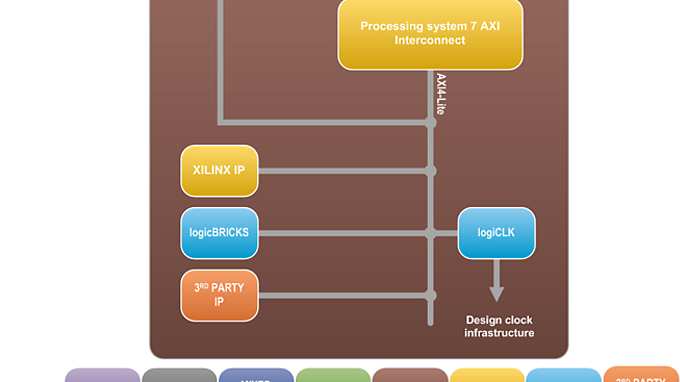

- HSSL IP 核(HSSL #0)可以通过 PS 7 AXI 互连访问所有 SoC IP 核的寄存器集

- HSSL 控制模块可以通过相同的 AXI 基础设施访问内部 HSCT、HSSL 和 BCU 寄存器空间

- HSSL IP核可以通过PL-PS接口上的GP和HP AXI3端口访问PS寄存器空间和板载内存

- 可编程 logiCLK IP 核可动态更改时钟,并支持将 HSSL IP 核设置为所需的波特率

英飞凌技术支持

- 请使用您公司的电子邮件地址在 myinfineon.com(超链接)下注册

- 将登录名发送至: AURIX@infineon.com

- 注册后,将为新文档提供自动更新服务

- 完整的注册过程最多可能需要 24 小时才能完成(由于时区不同)。

英飞凌科技股份公司、赛灵思公司和Xylon , doo合作以便在汽车和工业应用中更灵活地使用安全微控制器。Xylon 的全新 IP 核可通过英飞凌高速串行链路 (HSSL) 实现英飞凌 AURIX 系列微控制器( TC2xx和TC3xx )与 Xilinx SoC(片上系统)、MPSoC(多处理器 SoC)和 FPGA(现场可编程门阵列)设备之间的高速通信。该串行链路支持高达 320 Mbaud 的波特率,净有效载荷数据率高达 84%。

新的 IP 核将允许系统开发人员将AURIX™提供的功能安全性和安全性与 Xilinx 设备带来的广泛功能可能性结合起来。 链接的设备可以通过 HSSL 访问和控制彼此的内部和连接资源。

- 目前支持 Xilinx 7 系列和 Zynq-7000 SoC 设备系列

- 计划在不久的将来支持 Xilinx UltraScale、UltraScale+ FPGA 设备和 Zynq UltraScale+ MPSoC。

- HSSL从属设备

- 波特率高达 320 Mbaud/s

- 符合 ARM AMBA AXI4-Lite 总线协议,可作为从属设备

- 符合 ARM AMBA AXI4 总线协议的主设备

- 3.25 GB 的可寻址空间涵盖以下访问:

- FPGA 结构寄存器和 RAM

- PS 部分寄存器空间和 OCM

- 板载线性可寻址 FLASH 设备

- 板载 DDR 内存

套件描述

logiHSSL-ZU FPGA HSSL 入门套件 设计为系统设计人员提供了所需的一切,以便通过英飞凌高速串行链路 ( HSSLAURIX™ ) 快速将英飞凌的 微控制器与 Xilinx 全可编程 FPGA 和 SoC 设备互连。这些设备的组合解决了新兴汽车和工业设计中日益增长的安全性和性能要求。

套件内容

- 结合英飞凌的AURIX™微控制器和赛灵思的 UltraScale+ MPSoC 可编程设备

- 集成针对 Xilinx FPGA 实现优化的英飞凌高速串行链路 ( HSSL )

- 包含带有评估logiHSSL IP 核的完整参考设计

- 设计已为 Xilinx Vivado ®设计套件做好准备

- 链接的设备可以访问和控制彼此的资源

- 完整的硬件平台包括:

- 1 个 Xilinx Zynq UltraScale+ MPSoC ZCU104 评估套件

- 1x 英飞凌 Aurix 评估板套件KIT_A2G_TC397_5V_TRB_S

- 1 个 Xylon FMC 板用于电缆连接

1根FireWire线缆

- HSSL IP 核(HSSL #0)可以通过 PS 7 AXI 互连访问所有 SoC IP 核的寄存器集

- HSSL 控制模块可以通过相同的 AXI 基础设施访问内部 HSCT、HSSL 和 BCU 寄存器空间

- HSSL IP核可以通过PL-PS接口上的GP和HP AXI3端口访问PS寄存器空间和板载内存

- 可编程 logiCLK IP 核可动态更改时钟,并支持将 HSSL IP 核设置为所需的波特率

英飞凌技术支持

- 请使用您公司的电子邮件地址在 myinfineon.com(超链接)下注册

- 将登录名发送至: AURIX@infineon.com

- 注册后,将为新文档提供自动更新服务

- 完整的注册过程最多可能需要 24 小时才能完成(由于时区不同)。

图片库